在电源方面,找到一种提高功率密度的方法(即单位体积内产生更高功率)可实现许多关键设计优势,包括更小尺寸、更轻重量、更高效率以及更低物料成本。毋庸置疑,许多设计者选择电源元件时,将功率密度视为最重要的指标之一 。

在典型的动力系统中,设计者通常期望能改善功率密度之处就是Power MOSFET。近年来,半导体公司在这些元件的功率密度方面做出了极大地改进,但设计者们仍试图继续改善已存在的问题。

近期设计的新元件-快捷 FDPC8011S power clip 33 非对称 dual MOSFET表明仍有方法可以极大地改进功率密度。本文论述了 power clip 33 设计团队研究于更小封装内实现更高效能的设计思路。

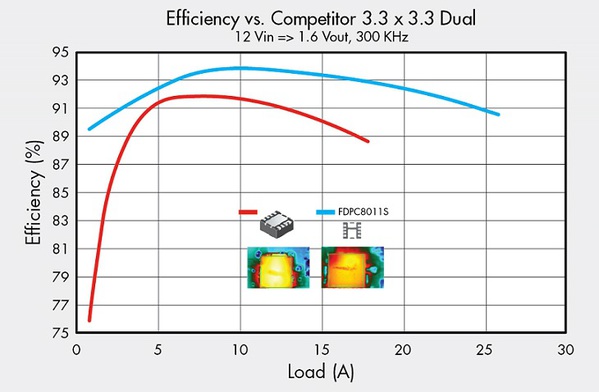

图1显示了power clip 33框图,图2中显示了与同尺寸(3.3x3.3mm)MOSFET相比,FDPC8011S 能够处理 8A 的额外负载且 TJ 温度低 6°C。

| 图一 : Power Clip 33 Dual MOSFET |

|

| 图二 : The Power Clip 33 与同类产品 3.3x3.3 Dual MOSFET |

|

Power Clip 33 封装

Power Clip 33 是一款双晶粒(dual-die)封装,将最佳品质因数 (FOM) 的矽材料与具备最佳热效能、低电感的铜片 (Copper Clip) 互连封装完美结合。图 3 显示了封装结构的关键要素。

高侧 (HS) MOSFET 汲极向下。低侧 (LS) MOSFET 源极向下。透过较大的铜片将高侧源极与低侧汲极互联。

如图4所示,相较于传统的封装设计(比如分立式 Power 33、Power 56 及 Power Stage 56 Dual),Power Clip 封装显著改善了寄生电阻和寄生电感效应。

最小化电源电路寄生效应

为了使同步降压动力系统实现最佳开关速度,设计时,在高频(HF) 开关路径中必须最大限度地降低封装寄生电感(封装中的开关路径为从V+ 引脚到SW 再到GND 引脚)。此外,设计中还必须最大限度地缩短 V+ / GND 输入电容及 MOSFET 封装引脚间的距离。透过使用一个汲极向下的高侧 MOSFET、晶粒间(die-to-die) Clip 和一个源极向下的低侧 MOSFET,Power Clip 的 IC 组态可实现上述两个目标。这使高频电源开关路径实现了最低阻抗,且无需封装接线。电源路径中唯一互联点是低电感/低电阻铜片。

增强的热效能

为了提高功率密度,热效能必需最佳化。在典型的 PCB 设计中,电路板铜片的两个较大区域用于布置 V+ 和 GND 引脚。汲极向下的高侧 MOSFET 和源极向下的低侧 MOSFET 的 Clip 设计可将封装中的大片区域与电路板铜片的这两大区域相连。铜片可有效支援晶粒间(die-to-die)的热耦合。这使两个晶粒均能实现较低的热阻抗 RΘJA ,无需考虑之间的功率分流。

先进的矽技术

此设计中采用的 MOSFET 技术为遮罩闸极 PowerTrench 技术。高低侧 MOSFET 设计均采用了低 RSP(mΩ/单位面积)及低闸极电荷 (QGD) 矽技术 两个元件均具备非常低的品质因数 (FOM) (依据 QGD*RSP 来确定)

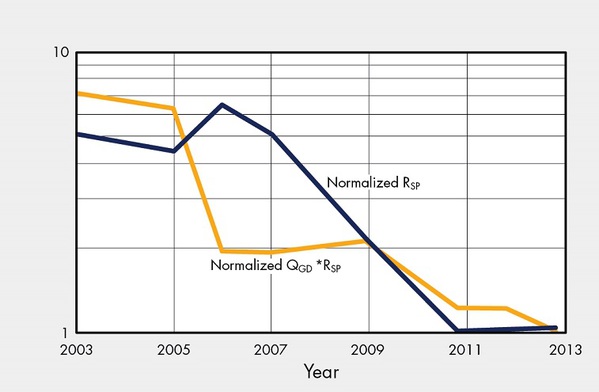

图 5 显示了快捷 RSP 及品质因数 (FOM) (QGD*RSP) 随时间推移不断提高。

| 图五 : RSP 及质量因子 (FOM) (QGD*RSP) 随时间推移而不断改进 |

|

随着时间的推移,快捷半导体不断改进这两项参数,且效果显著。传导损失 与 RDS(ON) 成正比,开关损失与 QGD 直接相关。对于 RDS(ON) 一定的 MOSFET,随着其品质因数 (FOM) 下降,QGD 及开关损失亦随之下降。快捷半导体在设计上的改进使这两项损失因素均有下降。

随着 RSP(单位面积的电阻值)下降,快捷半导体能够为典型的动力系统级设计更小尺寸的晶粒。晶粒尺寸下降可使 QG 及 QGD 下降。更小的晶粒尺寸亦可实现更小的封装,从而降低封装寄生效应。最终实现低开关损失及小型封装设计。

POL 转换器最佳布局

由于能够最大限度地降低电源回路面积及电路板空间,Power Clip 33 MOSFET 有助于实现电路板布局最佳化并提高系统效能。图6显示了使用 Power Clip 33 MOSFET 封装元件的电路板布局范例。

此高效能、高频率封装可为整个动力系统设计实现非常小的封装尺寸。 MOSFET、输入电容、电感和输出电容均布置到非常小的区域内。小型动力系统采用占位面积最小的开关节点,这可减少来自开关节点 (SW)的电磁干扰 (EMI) 杂讯辐射。

封装底部焊盘外露的 GND 及 V+ 引脚从 MOSFET 接面到电路板铜片及周围环境形成有效的热耗散路径。

为使封装实现最小寄生效应、最佳开关效能,输入电容及封装 V+ 至 GND 引脚间形成小型回路至关重要。 Power Clip 封装 V+ 及 GND 布置最佳化可实现非常紧凑的输入电容布置,最大限度地减小回路面积,从而减小寄生电感及开关损失。

如图7所示,采用 Power Clip 设计,高频开关回路面积显著减小。开关切换期间(低侧关断切换至高侧导通,或者高侧关断切换至低侧导通),电流必须迅速从一个 MOSFET 移至另一个。由两个 Power MOSFE 及输入电容组成的回路中会出现上述电流换向。相较于输出电感中的纹波电流频率,此回路中的开关瞬变要快得多。因此,这一回路决定了开关损失。

采用两个离散式 MOSFET,开关电流必须流经整个高低侧封装,再返回至输入电容。而采用 Power Clip 封装,电流则在封装一侧非常紧凑的回路中(仅间隔两个引脚的距离)流进流出。采用两个离散式 MOSFET 的布局中,高侧回路大小受限于 MOSFET 的封装大小。而采用 Power Clip 封装,回路大小目前受限于输入电容的大小。

结论

Power Clip 33 验证了在功率密度方面仍具有优势。 Power Clip 33 结合了先进的矽技术及改进的封装技术,显著降低了封装的寄生效应并在功率密度(A/mm2) 效能方面极大地超越了前代离散式产品,包括Power33/Power56 和Power Stage 56 dual 组合产品。

请注意,本文仅做简略概述,完整版对 Power Clip 33 与传统设计在效能、功率损失、波形、温度及热阻抗方面的实验室测试结果进行了详细比较。若要流览完整版文章,请移至快捷半导体网路研讨会中的「Power Clip 33 非对称 Dual MOSFET 如何在负载点应用中实现更高开关频率之解决方案」。