回顾2012年初,大陆手机业者打出「蓄4待发」的规格口号,亦即4核处理器、4吋以上萤幕、4G通讯(指LTE,但真正4G通讯应为LTE-Advanced)及Android 4.0作业系统。

而2013年,业界开始提出新一波主打规格,其中手机处理器被高度预估将有8核发展,若此属实,则纯就核数而言,已比一般PC处理器所用的核心更多(2~4核),可谓达伺服器水准,到底手机是否需要达8核水准?以下将从技术角度进行探讨。

多核不等于高效能

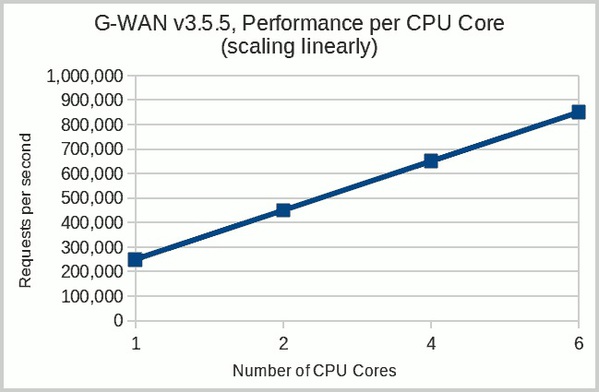

核心数的增加,不代表运算效能也线性增加,而是逐渐趋缓的走势,在相同时脉、相同制程、相同微架构的电路设计等前提下,若单核晶片的效能为100%,则双核晶片的效能不会是200%,而是低于200%,原因在于2个核心必须对运算工作进行沟通协调,协调即会造成效能损耗。

若要减少核心间的协调耗损,则需要传输量大、路由绕径智慧化的晶片内汇流排(On-Chip Bus),好的汇流排设计可以减少损耗,如双核可达170%效能,协调耗损为30%,差的汇流排则高损耗,双核仅有140%效能。

随着晶片内核数的增加,每增加1个核所能带来的边际效能将递减,假若单核为100%效能,追加第2核可再加70%效能,但再追加第3核恐仅再加60%,第4核更只有50%,将4个核加总的结果是100+70+60+50=280,即4核的真实效能仅为2.8核。

此为单纯硬体电路方面的效能估算,不代表软体实际执行所发挥的效能,倘若手机作业系统不能对多核进行最佳化编译,不能即时、充分发挥硬体功效,则效能还必须再往下打折扣。举例而言,Windows Phone 7.x版的手机作业系统仅能支援单核,即便采行双核手机晶片,依然只能发挥单核功效。

如果晶片电路能在愈多核的情况下,其协调折耗仍然很少,学理上称为效能的扩展延伸性(Scalability)佳,再将作业系统,甚至是作业系统之上的资料库、虚拟机器、应用程式等一并考虑,这些软体也必须同样具有扩展延伸性,如此效能才能获得充分发挥,此称为真实应用效能(Real Application Performance),而不是只在特有的基准标竿(Benchmark)测试上得到高分。

| 图一 : 最理想的多核效能扩展延伸是线性扩展(Scaling Linearly),每增加1个处理核心,均可增加100%的效能,然此在实务上几乎不可能,至多在基准标竿测试中出现逼近结果。(图片来源:gwan.com) |

|

多核的功耗挑战

增加核数除对效能有影响外,功耗用电也会受影响,每增加1个核,意味着核的用电增加1倍,双核为2倍用电,8核便则8倍用电。

为了减少耗电,晶片业者着手更智慧化的省电设计,采行如同家庭与办公大楼类似的省电手法,凡没有在用的房间立即关灯,减少照明用电。类似的,多核晶片把晶片内的多个电路功效划分成一个个的岛区,当软体不支援多核执行时,就把多核的供电关闭,仅提供单核供电,或需要多少个核执行即对多少个核提供电力,以此精省晶片的整体电能。

这样还不够,晶片业者发现晶片的运作时脉每增加10%,功耗则高至20~30%,用电量呈指数性攀升。为了节省电能,许多产品的CPU多以降频方式执行,如ASUS Eee PC与Apple iPhone等,在时脉上都降低30%,但电能却可精省至50%,以此增加电池使用时间。

进一步的,晶片业者也发现愈是高阶制程架构的处理核心,在重度运算负荷下的用电效益较佳,一旦处于轻载状态,反有较高的基础电能开销。因此,新的行动用晶片除了单纯增加核心外,也加入较初阶的处理核心。

1. 高低组态核心搭配趋势

例如TI OMAP4晶片在配置2个Cortex-A9核心外,也配置2个Cortex-M3核心,一旦晶片处于轻载(轻运算负荷)状态,则关闭对A9核心的供电,仅交由Cortex-M3核心执行,而在负荷变重时才唤醒A9投入运算。

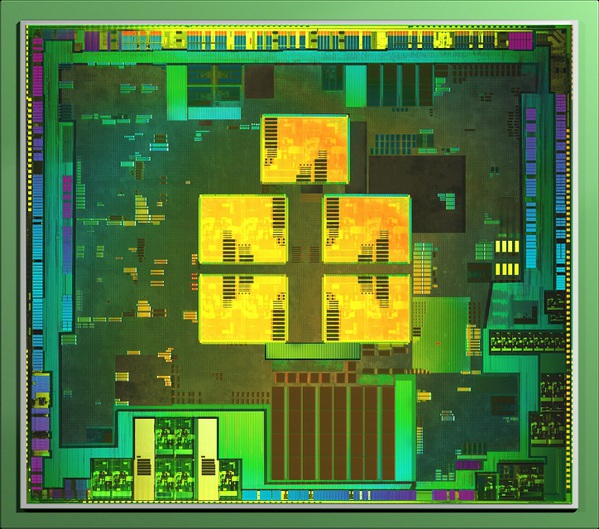

类似的,TI OMAP5也延续类似设计,采行2个Cortex-A15与2个Cortex-M4,或如NVIDIA Tegra 3晶片,一般在行销上宣称为4核晶片,但实际上晶片内配置了5个Cortex-A9核心,其中第5核心以较低时脉运作(500MHz,另4核为1.2GHz~1.6GHz),在轻载状态下使用,功效角色类似OMAP4中的Cortex-M3,也类似OMAP5中的Cortex-M4。

由于高低组态搭配已成了「为追求省电而不得不采行的设计趋势」,因此手机处理核心的领导业者ARM也提出官方版的高低搭配设计,称为big.LITTLE技术,提出以Cortex -15(重载)与Cortex-A7(轻载)搭配的高低组合。

事实上,目前最受关注、最可能率先推出8核设计晶片的业者是Samsung,侧面消息显示Samsung将推出的Exynos 5440即为8核晶片,内部的核心配置为4个Cortex-A15(1.8GHz)与4个Cortex-A7(1.2GHz)。

| 图二 : NVIDIA Tegra 3芯片的裸晶图,可明显看到中间5个Cortex-A9核心,其中有1颗以低频运作为主。(图片来源:NVIDIA) |

|

2. 即时动态调整频率

除高低微架构的核心搭配外,即时动态调整运作频率也成为「效能与用电」兼顾的手法,如Tegra 3在4核全开(不列计500MHz的低频)时每个核以1.2GHz时脉运作,但若仅1核运作时,时脉则可拉高至1.3GHz,时脉能拉高的原因有二,一是单核少去与他核沟通协调,可更加速执行,二是关闭多核后仅一核运作,晶片的功耗较低,发热较少,允许以较高时脉运作,因为温度也是晶片能否更高速运作的条件。

事实上,Intel的Turbo Boost技术即是侦测处理器晶片温度来自动决定晶片能否以更高频率运作,若温度升高至晶片难再承受的程度,便会尝试降低晶片的运作时脉,以缓和晶片持续高热的情况,待温度降至可承受的程度后,才再次调高运作时脉。

多核的制程议题

增加核数除了影响效能、功耗外,成本与体积(或称电路面积)也必须考虑。从制造层面考虑,则晶片电路面积几等于晶片成本,另再加外部的封装、测试成本,而采行更先进、更缩密的半导体制程,例如从40nm缩至28nm,则初期的光罩成本高昂,但晶片的量产成本却可降低,不过先决条件是新旧制程的良率一致,没有恶化,然新制程初期的良率较低。

在此还要提醒考虑另一成本,即处理核心的授权成本,依据ARM所订立的商业规格,每使用一种核心即必须先支付技术授权费,而后每颗晶片若有配置了该核心,则每颗都会被收取量产权利金。因此,核数愈多即表示要支付愈多费用给ARM,若采行不同类型的ARM核心,也必须再支付一笔使用他款核心的技术授权费。

一切为了行销

归结上述可了解,所谓8核并非是相同强悍规格的核心,而是重载型、轻载型高低搭配的核心,效能不仅不可能是重载单核的8倍,以半数核心均属轻载型的组态配置下,效能恐与现有4核重载设计相差无几,或是在轻载多核的运算需求下有较佳的表现。

不过,确实有晶片业者确实构想8个均为重载型核心的晶片,目前传闻MTK的MT6599晶片将是8个Cortex-A15核心,然如前所言,即便拥有8个核,效能也不会是单核的8倍,而是逐核递减。重载8核的设计,确实能比4轻核加4重核更有效能,但也可能更耗电,因此已知MT6599将采28nm制程生产,以新制程收敛功耗。

若无上述的技术,对一般终端消费者而言,仅以广告行销与规格型录研判,则认为8核拥有显著的效能提升,进而提高选购意愿,此正是手机晶片业者与手机业者所期望的,8核在规格行销上是个很好发挥的题材。

结论

最后,不仅手机处理晶片,各应用领域的处理晶片均朝多核化发展,原因在于持续精进处理器的微架构设计,所能带来的加速效益已经趋缓,且每更动一次设计,连带的后续验证程序过于繁复,经常有晶片已投片量产才发现设计有瑕疵错误,之后以韧体、软体方式去弥补,甚至回收晶片。另外以单核、少核晶片为基础,以提升运作时脉的方式获取效能,也一样碰上瓶颈。

相对的,由于半导体缩密制程技术的精进,且多核执行的编译器成熟发展,因此多核成了近年来处理器持续提升效能的主流手段,核心直接增加数目的好处是不用再对设计进行验证,因为过往已验证过,然缺点如前所述,晶片间的沟通协调成了新的效能瓶颈,因此多核晶片的后续技术精进,多聚焦在核心间的汇流排上。

往未来看,手机处理晶片的效能也将如个人电脑处理晶片一样,逐渐达到效能需求饱和的情景,且随Internet、云端应用的发达,晶片内外的传输通量将成为发展重点,晶片运算执行处理效能则退至次位要求,这样的趋势已逐渐到来。

(作者为CTIMES特约主笔)