随着越来越多的系统整合多个IC,系统功耗也不断增加,这是目前全球关注的问题。除了带来环保影响外,功耗增加也会增加系统构建及运营成本。想要散去多余热量,就必须使用复杂的散热片、风扇甚至更多的稳压器,而这些都会增加资本支出、运营支出。包括设备运行以及降温所需的电力,也会随着总功耗的增加而增加。此外,系统过热会降低可靠性,及增加系统停机风险,并提高运营成本。

28nm破除FPGA静态功耗套门

另一方面,摩尔定律的不断延续,新一代半导体制程技术都会提高整合度,以降低成本。不过,上述优势往往会被增加的静态功耗抵消。每次缩减外形尺寸,似乎不可避免地都会提升静态功耗,这种现象在FPGA产业中尤为明显。一直以来,FPGA产业在采用最先进制程技术为客户提供更高效能及容量方面一直处于半导体产业的领先地位。后来,系统设计人员发现,由于功耗原因,他们很难充分运用更高的密度和电路速度。支援新一代系统的关键在于为设计人员提供更高的「可用效能」,也就是说,要在可用功耗预算范围内提供尽可能高的资料处理能力。降低静态功耗可为动态功耗留下更多功耗预算,从而提高可用效能,进而也能提高介面频宽,并为同一FPGA中的逻辑、记忆体、DSP及其他功能提供更多资源。

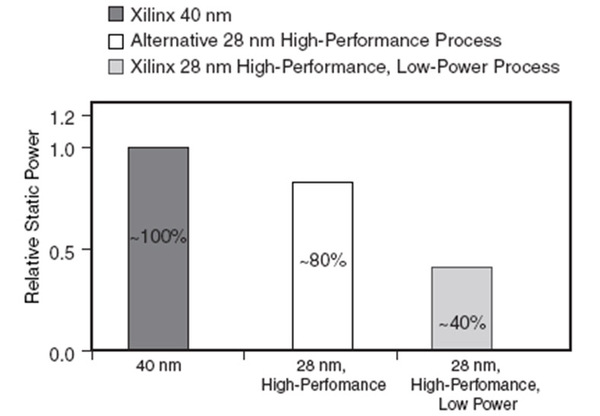

FPGA设计的关键挑战在于管理动态功耗的同时,控制静态功耗的提升,静态功耗完全是开销,对效能毫无助益。不幸的是,制程提升反而会增加静态功耗。事实上,在某些情况下,静态功耗的提升幅度还会超过动态功耗,参见图一。

在28nm节点出现之前,FPGA产业尝试透过降低电源电压和多重电晶体临界电压来解决功耗提升问题,并成功达成目的。不过,随着28nm制程出现,就必须采用新的方法。

为了解决28nm制程技术的可用效能问题,开发了针对FPGA的HKMG高效能低功耗28nm制程技术。此最新28nm制程技术建立在40nm FPGA制程开发的成功基础上,并推出最新 HKMG技术,透过降低功耗能最大限度地提高可用的系统效能。该技术相对于其他制程技术而言,能大幅降低静态功耗。就28nm节点而言,静态功耗往往占元件总功耗的绝大比例。因此,要想最大化功率效率,制程技术的选择至关重要。

28nm FPGA制程技术:HKMG

传统的FPGA制程技术在28nm制程上已经达到功率极限,也达到效能极限。问题根源在于几十年来用于构建IC电晶体的多晶矽闸极和氧氮化矽闸极电介质(Poly/SiON)。

为了提高电晶体速度,半导体工程师一直在随着制程技术的提高努力减小闸极介电层的厚度。不过,由于介电层通道效应和闸极本身的漏电流,电介质厚度减少会导致漏电流增加,这就会造成制程技术每次节点进步都会大幅提升静态功耗。

新一代FPGA以三重闸极氧化层电路技术成功控制隧道电流效果,从90nm制程到 40nm 制程节点一直都比较成功。不过,就28nm制程而言,闸极氧化层太薄,必须用最新闸极材料和架构来处理隧道效果。为了控制闸极下的漏电流(低于阈值的漏电流)。

为了解决28nm制程问题,采用了二氧化铪这种新型闸极介电材料,该材料的介电常数(κ)较高,可增减闸极厚度,这就使电晶体不太容易受到隧道电流效应的影响。举例来说,40nm 制程使用的二氧化矽κ值为3.9,而28nm 金属闸技术所用的二氧化铪κ值则为25,这就成为高效能低功耗28nm制程技术的最佳选择,如图二所示。

仔细评估多种28nm制程技术,其中包括标准的低功耗(LP)和高效能(HP)制程,最后决定采用28nm HKMG高效能低功耗制程技术。 28nm LP制程是Poly/SiON 40nm技术的简单升级,风险较低,但该技术不适用于FPGA,因为其电晶体切换速度太慢,效能不够高;28nm HP技术专为实现高效能而最佳化,但又会造成功耗过高,也限制了可用效能,如图三所示。

| 《图三 40nm和28nm制程技术实现同样效能的静态功耗比较》 |

|

28nm HP制程技术还需要将HKMG与SiGe应变技术整合。两种高级技术在制造制程中整合,相对于采用HKMG和应力衬垫应变技术的高效能低功耗28nm制程技术而言,会存在更多风险。

解决两难困境:以更低功耗实现更高效能

FPGA设计旨在满足汽车、广播、消费、工业、医疗、测试与测量、视讯、有线通讯和无线通讯等不同市场的多种不同应用需求。 28nm FPGA产品是透过上述市场领域中众多客户的协助所定义而来,其目标就是降低一半功耗,而系统效能则提升一半甚至更高。为了满足28nm FPGA的介面效能要求,除大幅提升时脉技术,并决定加强关键资料路径元件,从而大幅改善外部记忆体介面,可将整体系统效能提升一半以上。

就许多高效能微处理器而言,最重要的设计特性就是原始的核心速度。与此形成对比的是,FPGA可以适当地翻转率执行高效能资料处理任务;设计人员可充分发挥FPGA架构内在的并行处理优势来建立较宽的资料路径,而时脉运行速度则远远低于输入输出线速。由于元件容量提升2倍,因此28nm技术能支援更高的流水线和并行处理能力,进一步提升核心效能。这类似于微处理器领域采用多核心设计的发展趋势,虽然每个核心的工作频率降低,但整体效能却超过单一一个高强度运行的核心。

除了高效能低功耗制程技术外,28nm FPGA还受益于时脉闸技术以及最新的布线演算法,可进一步降低功耗。精细时脉闸控技术(Fine-grain clock gating technology)是一种专利演算法,可分析逻辑方程式并禁用无益于最终结果的多余逻辑转换。由于删除不必要的逻辑工作,从而能将功耗平均降低 20%,如下图四所示。

通过验证的方法:加速 28nm FPGA 上市时程

对晶片测试工具的智慧使用,可确保在FPGA产品推出之前很早就做好技术准备,并对包括元件效能、设计/制程范围、晶片内建变化、制造设计(DFM)、关键模组验证、制程和产量稳定性、裸片-封装相互影响、以及最终产品可靠性等在内的所有领域进行全面检查。测试工具的效率要提升,必须确保重要的测试结构和设计/IP模组与元件和制程开发的重要时间节点相协调,而不能单纯关注开发制程中部署测试工具的绝对数量。

此一通过验证的技术开发方法包括四个阶段,如表一所示。

测试工具开发的四个阶段

第一阶段 |

制程开发/联合技术定义 |

第二阶段 |

分立电晶体、射频以及单元/阵列 |

第三阶段 |

电路层级/硬式 IP |

第四阶段 |

类产品结构 |

第一阶段开始时,制造合作伙伴将提供针对特定技术的测试结构,以执行新的制程模组,支援新设备推出,并评估新材料组合。举例来说,40nm制程使用浸润式微影技术和SiGe技术,而28nm制程则使用HKMG技术。

在第二阶段中,用更多测试工具,以验证如电感器和电容器(对高速收发器极为重要)以及以单元/阵列为基础的 FPGA 元件结构等射频元件。

在第三阶段,电路级FPGA模组(如模组RAM和配置)和硬式IP结构添加到测试工具中。这种测试可评估巨集级功能和特定FPGA模组效能,包括对电路效能的寄生效应。其他结构能在产品开发早期阶段就明确得知ESD效果特性。在一段时间内持续收集并检验工具的实践资料,将元件型号与实际的晶片技术互相关联,从而得到有助于提升效能、降低功耗的FPGA 解决方案。

第四阶段,包含之前各阶段测试工具的重要元件,并增加对代表性产品类结构的测试。举例来说,调试专门关联于FPGA产品布局效果随机问题的RAM,也对功能和效能进行描述,并能进行早期产品可靠性评估。

专利基准测试结构配合统计分析,有助于识别出突显关键制程中边缘性的薄弱点。其他结构均采用整体设计,可识别出制程和设计之间的相互影响,并对不同制程、电压和温度(PVT)条件下的前端(电晶体级)和后端(互联/电介质)效能及功耗进行早期分析。这种代表性的架构亦添加到FPGA元件中,对实际FPGA元件测试工具结构提供的结果进行进一步的调试和关联,如图五所示。

除了电容器和电感器等基本构建元件外,测试工具中还包括多PLL振荡器及其它电路,从而强调对收发器的关键元件。振荡器是收发器核心,需要早期全面的描述塑造,以确保频率稳定性,避免相位杂讯。边缘速率和回损等更多参数特征化也透过收发器相关结构完成。测试工具将多个结构彼此靠近放置,再结合全后端金属层,可识别潜在的耦合效果以及相邻振荡器间的相互影响。这种贴近性非常重要,因为FPGA中,带全后端金属层的多个结构与只有一个后端金属层的单振荡器特性不同。有关资料能在技术开发早期阶段就解决问题,并快速让28nm FPGA 准备就绪。

结语

功耗是现在半导体产业的首要关注点,在FPGA产业中功耗问题尤为突出,相对于前代FPGA而言,高效能低功耗28nm制程技术与架构创新,以及设计开发工具的结合,提供一种统一的的新方法。而28nm FPGA产品将能实现系统架构师和逻辑设计人员所需要的革命性突破。该技术使设计人员能开发出更广泛的FPGA应用,从低功耗应用(如HDTV、工业控制和车载资讯娱乐)到高频宽以及超高阶应用(如通讯设备、高效能计算、软体无线电和视讯处理)等,无所不包。