imec展示全球首次实验示范采用18nm导线间距的双金属层半镶嵌模组,强调窄间距自对准通孔的重要性,同时分析并公开该模组的关键性能叁数,包含通孔与导线的电阻与可靠度。

铜双镶嵌制程在业界长跑20馀载,能够稳定量产具备高可靠度的晶片内部导线。然而,随着元件面积持续紧缩,金属导线间距降至20nm以下,後段制程的电阻与电容(RC)因而大幅增加,加剧了电路传输延迟的问题。这就迫使相关产研单位去开发替代的整合方案与金属材料,优化窄间距金属导线的性能。

imec约在5年前首次提出半镶嵌制程的概念,作为替代铜双镶嵌制程的可行方案,用於1nm制程及其後续制程节点,整合不同金属层间的局部导线,实现互连。

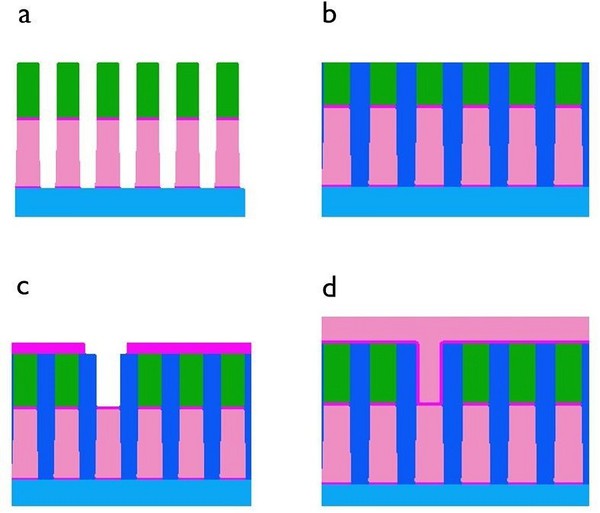

| 图一 : imec半镶嵌制程流程(a)??蚀刻,生成底部元件层的局部金属导线(Mx)(b)空隙填充(c)通孔蚀刻(d)通孔填充与生成金属层之上(Mx+1)的顶部元件层。 |

|

不同於双镶嵌制程,半镶嵌整合技术以直接图形化的方式制造内部金属导线,这也称作减法导线制程(subtractive metallization),亦即蚀刻,过程中金属导线不需经过化学机械研磨(CMP)。负责连接不同导线层的通孔采用单镶嵌制程制造,随後以金属填满後继续填充,也就是说持续沉积金属材料,直到介电层上方生成一层金属层。该金属层接着进行微影蚀刻,以制成第二层导线层,形成一条垂直的互连导线。完成金属导线的图形後,元件层上的空隙可以用介电材料填充,或是当作局部元件层的(局部)气隙(airgap)结构。

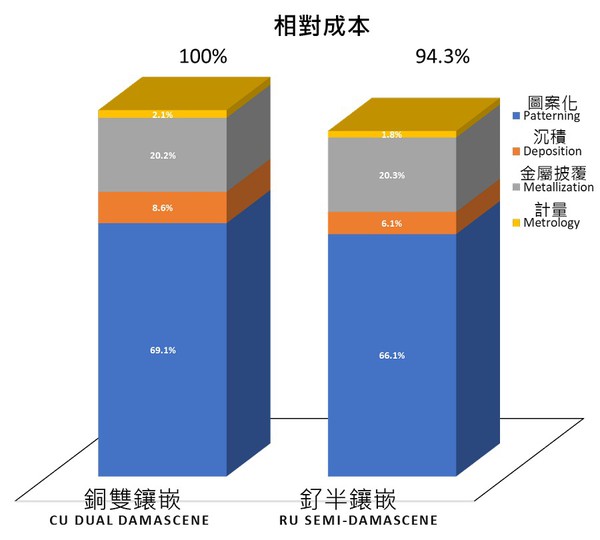

值得注意的是,在半镶嵌制程中,通孔与顶部金属层会同步制造,与传统的双镶嵌制程相同。因此,相较之下,半镶嵌制程更有效率,具备低成本的竞争优势(见图二)。

| 图二 : 比较半镶嵌与双镶嵌制程在制造金属导线间距18nm元件时的成本结构。 |

|

半镶嵌制程的优势

在制造窄间距金属导线时,半镶嵌制程具备几项优势,胜过双镶嵌制程。imec研究员暨奈米导线研究计画主持人Zsolt Tokei表示:「第一,半镶嵌制程能制造高深宽比的导线结构,同时控制电路的电容,有利於降低整体的RC延迟。第二,可以省去金属导线的化学机械研磨步骤,实现简便且低成本的整合方案。第三,半镶嵌制程需要可图形化又不需阻障层的金属材料,例如钨(W)、??(Mo)或??(Ru)。与铜镶嵌不同,采用这些金属材料不需要金属阻障层,如此一来,金属导线可以充分利用珍贵的导电区域,在微缩设计中展现优异的通孔电阻值。」

当然,除了这些优势,半镶嵌制程在获得业界采用前,仍有几项技术挑战必须解决。其中一站必经之路就是实际演练两层金属层之间的导线互连。虽然目前只能透过模拟建模来计算性能叁数,imec近期首次展示了双金属层半镶嵌模组的实验数据。

制程关键:全自对准通孔(fully self-aligned via)

在金属导线间距仅有20nm的情况下,半镶嵌制程的成功关键在於通孔蚀刻的精准度,必须恰好在狭窄导线的上方。倘若元件顶层与底层的通孔与导线未能对准,通孔与紧邻的导线之间就可能产生漏电流。这些漏电路径的产生源自传统图形化技术在制造微缩尺寸的通孔结构时的对准误差过大。

imec技术研究主任Gayle Murdoch表示:「制出性能完备又能全自动对准的通孔,一直是半镶嵌制程梦寐以求的技术。imec内部负责整合、微影、蚀刻与清洗技术研究的团队之间紧密合作,共同立下此次里程碑。利用我们开发的全自对准整合方案,通孔对准误差可以校正补偿的幅度高达5nm,成果斐然。」

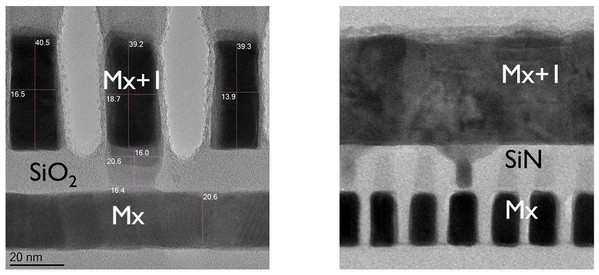

| 图三 : 自对准通孔沿着金属层(左)与横跨金属层(右)结构拍摄的穿透式电子显微镜截面影像(X-TEM),显示自对准通孔可以准确落在18nm间距的??导线上方。 |

|

在填充空隙後,可以透过移除局部的氮化矽(SiN)来确保底部元件层的通孔能够自行对准下方的导线图形。顶部金属层(??)的自对准通孔则利用过度蚀刻(over-etch)实现,在通孔过度填充并进行??金属图形化後,持续蚀刻出通孔图形。

全球首例18nm导线间距半镶嵌制程

利用减法制造对??金属进行蚀刻,并导入自对准通孔设计,最终能制出导线间距18nm的双金属层元件。底部??金属层(Mx)的导线宽度9nm,利用极紫外光微影(EUV)与自对准双重图形化(self-aligned double patterning;SADP)技术制造,金属层上方的顶层元件层(Mx+1)与通孔则采用单次曝光EUV制程。顶层导线还会搭配气隙结构,抵销电容增加对性能的影响。

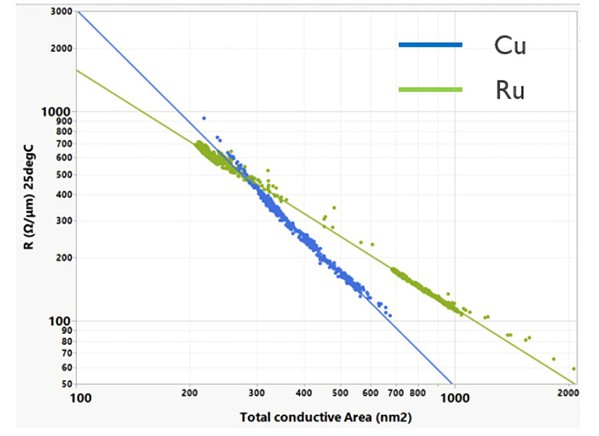

在比较??与铜的导线电阻与导电面积时,可以发现??在采用目标导线间距设计时的性能胜过铜。通孔的自对准性能也经过数学形象学与电学确认。研究结果显示,通孔电阻表现优异,导线间距为26nm~18nm时,可以控制在40?~60?的范围,通孔与导线之间的崩溃电场则是小於9MV/cm。

| 图四 : ??导线与铜导线的导电面积与电阻值比较。 |

|

Zsolt Tokei表示:「我们经过研究显示,半镶嵌制程在所有的关键性能叁数方面呈现绝隹表现,包含通孔与导线的电阻与可靠度。此次实验结果表示,半镶嵌制程能够代替双镶嵌制程,用於1nm制程或後续制程节点,整合前三层的局部导线层。此次我们开发的双金属层元件导入自对准通孔技术,证实是半镶嵌制程的关键。」

未来可以透过增加导线的深宽比(降低电阻),同时维持气隙结构(控制电容)来提升元件性能。与此同时,imec对中段与後段制程也有明确想法,能导入制程方案来推动半镶嵌制程进一步发展,进而从标准元件层级缩小元件尺寸。

(本文由imec提供;编译/吴雅婷)