现今,许多主流处理器应用软件对效能的需求越来越高,以处理更高的数据传输速率、更多的媒体服务,与利用用户接口的新功能,如:加密与安全防护。在应用市场中,当消费者需求成为产品开发的主要动力,供货商将面临降低终端产品价格的挑战。这不只是为了在既有市场竞争,而是在可支配所得远低于西方国家的开发中国家中,开创新的市场。

有许多例子指出,联网行动计算机、其他便携设备、手机、PDA、视频转换器、游乐器,以及汽车信息娱乐装置等应用,都需要低成本且高效能的特性。

消费者不仅期盼他们的产品能执行更多功能,更希望可携式产品能具备更长的电池续航力。为了达到可以连续使用一整天的最低要求,手机、智能型手机以及PDA制造商必须提供比以往更高的效率及超高效能。以智能型手机为例,其应用效能需求从待机时的「非运作」状态,到执行游戏时的高运作模式,其系统架构必须能够因应两种极端的效能需求,同时维持极高的效率。

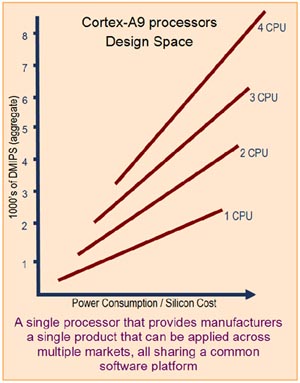

其中一种方法是使用多重核心处理器架构,来满足尖峰效能的需求,并让设计方案能因应极低功耗的运作模式。多核心组件具备极高的扩充效能及低功耗的特性,故能提供相当优异的设计弹性。

Cortex-A9 MPCore多核心处理器

Cortex-A9 MPCore多核心处理器整合了成熟且极为成功的ARM MPCore技术与后续的改良,简化并扩展多核心解决方案的应用。Cortex-A9 MPCore把尖峰效能提高到前所未有的层次,并在同时支持设计弹性与各种新功能,从处理器与系统层级着手,进一步降低与控制功耗。

Cortex-A9 MPCore针对的产品,也为行动装置带来超越现今解决方案的优异尖峰效能,利用ARM MPCore的设计弹性与先进电源管理技术,在紧缩的行动电力预算下维持运作。

利用可扩充的尖峰效能,这款处理器的效能能够超越现今同级的高效能嵌入型组件,并为更广泛的市场带来持续的软件投资。

| 《图一 Cortex-A9 处理核心的设计空间区隔》 |

|

满足多重市场的需求

Cortex-A9处理器为各种市场应用提供可扩充的解决方案,从手机市场到高效能的消费性与企业级产品,Cortex-A9处理器都能满足以下共同需求:

- ●达到更高的效能,并提高能源效率,藉以降低功耗

- ●替要求最严苛的应用提高尖峰效能

- ●让多种组件能共享软件与工具投资

Cortex-A9处理器不仅维持完全的应用兼容性,也运用了Cortex-A9 NEON媒体处理引擎(MPE),或浮点运算单元(FPU)来提升特定应用的效能,进一步扩展这些处理器的市场应用范畴。每种建置的设计组态,都能够提供充裕的弹性,以适应不同的应用与市场特性。

(表一) Cortex-A9 处理器应用范例

新一代装置 |

Cortex-A9解决方案 |

手机、联网行动计算机 |

新一代高阶装置(1500-3000DMIPS)

- 2至3个内建IEM技术与可调适关机功能的处理器

- 32K指令与数据快取,256至512K共享L2快取,运用PL310、可分区AXI

- NEON技术的媒体处理引擎,搭配GPU

|

中阶、降低成本(900-1500 DMIPS)

- 单核心处理器搭配NEON或浮点运算单元

- 16K或32K指令与数据快取

- 128-256K L2快取,使用PL310、单AMBA AXI总线

|

多功能的量产市场(600-900 DMIPS)

- 内建浮点运算单元的单核处理器

- 16K指令与数据快取、单AXI

|

消费性与汽车信息娱乐装置 |

消费性产品:用户互动功能(800-3000 DMIPS)

- 1至4个核心处理器,支持系列装置的设计扩充性

- 32K指令与数据快取,搭配0至512K L2快取

- 支持先进媒体与DSP处理作业的NEON技术

- 先进总线接口单元,能在芯片内部的3D引擎与网络接口MAC之间进行高速的内存传输作业

- AMP组态,让实时RTOS使用不同的CPU

|

网络/家用网关 |

企业市场(4000-8000 DMIPS)

- 3至4个核心的效能优化方案

- 32K+64K指令与数据快取

- 512K-2MB L2快取,两个64位AMBA AXI介面

|

消费性装置(800至1500 DMIPS)

- 运用附属加速器的1x或2x多核心组件

- 32K+32K指令与数据快取,搭配256-512K共享L2快取

- NEON或VFP,协助提供媒体网关或服务

|

嵌入型产品 |

嵌入型媒体与图像处理(800至2000 DMIPS)

- 2x多重核心组件,运用附属加速器

- 32K+32K指令与数据快取,搭配256K共享L2快取

- 浮点运算单元支持postscript档案以及图像处理与强化功能

- 透过特定的AMP/SMP建置方案移植程序代码

|

特殊应用优化

Cortex-A9 与Cortex-A9 MPCore 应用等级处理器,皆具备ARMv7架构功能以及其他丰富特色,能针对特殊应用与一般用途的设计,带来高效能与低功耗的解决方案。

(表二) Cortex-A9 处理器特色

功能特色 |

优势 |

高效率超纯量管线 |

超过2.0 DMIPS/MHz的业界领先效能,不仅带来前所未有的尖峰效能,还维持低功耗的效益,藉以延长电池续航力、低成本的封装与运作模式。 |

NEON 媒体处理引擎 |

加快媒体与讯号处理功能,以增进特殊应用效能,带来汇整应用软件研发与支持的便利。 |

浮点运算单元(FPU) |

大幅加快单倍与双倍精准度纯量运算作业速度。效能比前一代的ARM 浮点运算单元高出一倍,此单元提供领先业界的图像处理、绘图,以及科学运算能力 |

优化的Level 1 快取 |

具备优化效能与功耗的L1快取,结合最低存取延迟技术,提高效能并降低耗电量。同时提供快取连贯性的选项,以改进处理器间的通讯,或支持丰富的SMP操作系统,达到简化多重核心的软件开发作业的目标。 |

Thumb-2 技术 |

减少30%储存指令时所使用的内存,并提供传统ARM程序代码的尖峰效能。 |

TrustZone 技术 |

确保可靠地建置各种从数字版权到电子付费的安全应用,并提供技术与产业伙伴的广泛支持。 |

Jazelle RCT 与DBX 技术 |

在及时与提前编译字节码语言程序代码时,让程序代码长度减少3倍,并支持直接执行Java指令程序代码,藉以加快传统虚拟机的速度。 |

L2 快取控制器 |

支持各种高频率,或需要降低功耗以存取芯片外部内存的设计,提供低延迟、高带宽模式存取高达2 MB的高速缓存。 |

程序追踪宏与CoreSight 开发工具包 |

结合这些组件,让软件研发业者能以不干扰的方式追踪多个处理器的执行历史,并同时与时戳修正数据,一起储存到芯片内缓冲区,或透过标准追踪接口储存到芯片外部组件,藉此改进开发与除错阶段的可视性。 |

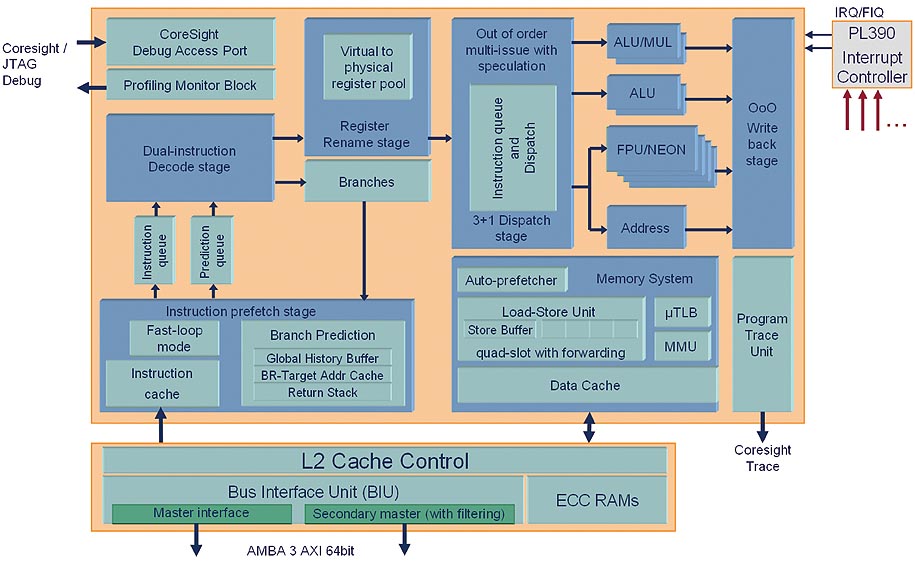

先进的微架构

精心设计的Cortex-A9微架构,针对追求低硅组件成本的嵌入型组件,提供最大化的处理效率,并排除超高效频设计缺少效率的缺点。透过各种合成技术,该处理器能让组件能达到超过1 GHz的频率频率,并提供超高的省电效率,进而带来更长的电池续航力。

| 《图二 Cortex-A9 微架构的结构以及单核接口》 - BigPic:914x563 |

|

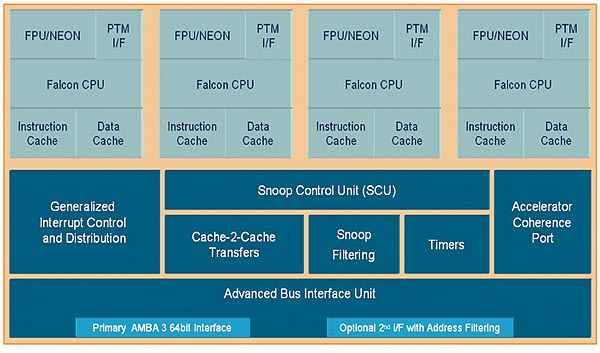

Cortex-A9 MPCore技术

Cortex-A9 MPCore多核心处理器提供一个设计组态的处理器,利用整合快取的协调方式支持1至4个CPU。每个处理器能独立设定自己的快取容量,并决定是否支持浮点运算单元、MPE、或PTM接口。此外,任何组态的处理器都可链接加速器链接埠( Accelerator Coherence Port),允许其他无快取的系统主控端外围组件与加速器,如:DMA引擎或加密加速器核心,链接至处理器的L1快取。Cortex-A9 MPCore还整合一个兼容整合中断的中断控制器架构与通讯系统,搭配专属外围组件,用来提高效能与软件可移植性,并可被组态以支持0(旧型旁通模式)或224个独立中断来源。这个处理器也能支持单一或两个64位AMBA 3 AXI互连接口。

| 《图三 Cortex-A9 多核心处理器》 - BigPic:599x352 |

|

Cortex-A9 MPCore多核心处理器包含一个以通过硅实体验证的ARM MPCore技术增强版,能够支持可扩充的多核心处理功能:

侦测控制单元(Snoop Control Unit, SCU)

侦测控制单元是ARM多核心技术的中央控制核心,在所有搭载MPCore技术的处理器中,负责管理互连、仲裁、通讯、快取之间与系统内存的数据传输、快取链接、以及其他多核心功能。

Cortex-A9 MPCore处理器首度将这些功能扩展至其他系统加速器及非快取的DMA外围组件上,让各组件共享处理器的快取架构,以增进效能并降低整个系统的耗电量。这项系统不但链接设计,亦因不必维护每个操作系统之间的软件关联性,而降低软件的复杂度。

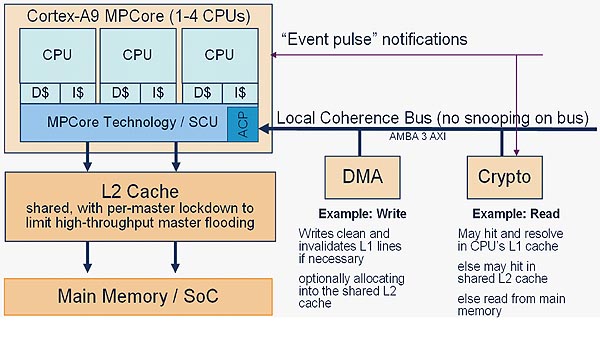

加速器链接埠(Accelerator Coherence Port)

在SCU上的AMBA 3 AXI兼容从属端接口,为各系统的主控端提供一个互连点,使整体系统效能、功耗,或是其他软件简化因素,能够更直接地与Cortex-A9 MPCore处理器接口链接。此接口扮演标准的AMBA 3 AXI从属端,并在对链接组件无额外相关要求的条件下,支持所有标准的读取与写入交易。

然而,任何接触到内存中关联区域的读取交易,都会和SCU进行互动,以测试要求的信息是否已储存在处理器的L1快取。若信息已存在快取内,就会直接传回到发出要求的组件。若数据没有储存在L1快取,在转到主存储器前,仍有机会搜寻L2快取。接触到任何关联内存区域的写入交易,SCU会在动作被转至内存系统前,执行链接。写入交易也可转至L2快取,藉以排除因直接写入芯片外部内存而衍生的功耗与效能影响。

| 《图四 加速器的链接埠》 - BigPic:599x350 |

|

中断控制器(Generic Interrupt Controller)

运用最近完成标准化与架构化的中断控制器,GIC提供丰富且弹性的方法建构处理器之间的通讯,以及系统中断的传递与优先排序机制。在软件控制下最多可支持224个独立中断,每个中断能在CPU,硬件优先排序,以及操作系统与TrustZone软件管理层之间传递。这样的传递路径弹性,加上支持操作系统的中断虚拟化机制,创造了一个关键功能,让使用半虚拟化管理器的解决方案能够强化其功能。

先进的总线接口单元

Cortex-A9 MPCore处理器强化了处理器与系统之间的接口互连,提供许多先进功能,达到系统效能最大值,并针对各种系统单芯片设计方法带来额外的弹性。

透过支持单倍或双倍64位AMBA 3 AXI主接口的设计组态,处理器能在CPU速度下提供全负载的交易平衡机制,支持速度超过12 GB/s的系统互连接口。第二个接口亦可定义成处理全局寻址空间的交易过滤器,为系统设计增加弹性,在处理器架构中立即分割寻址空间。

每个接口亦提供不同的CPU与总线频率比,包括同步半频率比,藉以替支持采用DVFS或高速芯片内存储器的设计增加设计弹性,并改进系统带宽。此外,产品还可完全支持ARM智能型电源管理(IEM)功能。

运算引擎加速功能的特定应用

除了各项优化的标准架构功能外,Cortex-A9与Cortex-A9 MPCore处理器皆能支持以下功能:

先进的L2 快取控制器

ARM L2快取控制器 (PrimeCell PL310)与Cortex-A9处理器一起研发,提供一个优化的L2快取控制器,能配合Cortex-A9处理器的效能与总处理能力。

PL310的每个接口能支持高达8个未完成的AXI交易,加上每个主控端与方向的锁定机制,能透过加速链接埠在多个CPU或组件之间进行管理分享,有效运用PL310作为加速器与处理器之间的缓冲区,增进系统效能并降低相关功耗。

PL310亦含有Cortex-A9先进总线接口单元的各项功能,故能支持同步式1/2频率周期比,以降低高速处理器设计的延迟,且能对第二个主控端AXI接口进行地址过滤,以支持分割区域、分割频率的设计,并快速存取芯片内的暂存内存。

PL310最高可支持2MB的4至6路关连式L2高速缓存,支持与同位与ECC支持RAM的选项性整合,并在处理器的频率频率下运作。先进的锁定技术亦提供许多运用高速缓存以作为链接加速器与处理器之间的传输RAM的机制。

Cortex-A9程序追踪宏 (PTM)

Cortex-A9 PTM为Cortex-A9处理器提供与ARM CoreSight技术兼容的程序流程追踪功能,能监看处理器实际的指令执行流程。Cortex-A9 PTM能搭配周期计数功能,监看所有程序代码的分支和程序流程的变动,以便进行设定分析。

此外,Cortex-A9 CoreSight开发工具包能链接多个处理器的追踪流程,且含有CoreSight组件,以对Cortex-A9 MPCore多核心处理器设计进行追踪与除错。

合成弹性与参考设计方法

Cortex-A9处理器充分利用合成设计流程的弹性,能针对任何晶圆制程与尺吋。透过持续与各大EDA厂商合作,以及各种实作参考设计方法(iRMs),Cortex-A9处理器的授权客户能针对自己选择的制程技术,对处理器进行客制化、建置、检验,及特性规划。这些参考方法提供可预测的硅组件开发路径,作为发展客制化设计方法的基础,利用各种逻辑与实体合成技术。

除了iRM外,还可加入ARM Artisan前端组件库检视功能,以及预先编译的RAM,来强化iRM提供处理器建置流程的功能,并提供远比先前更完整的参考解决方案。

(表三) Cortex-A9的FPU与MPE功能说明

Cortex-A9 浮点运算单元 (FPU):

|

Cortex-A9 NEON 媒体处理引擎(MPE):

|

在搭配Cortex-A9处理器时,FPU提供高效能的单倍及双倍精准度的浮点运算指令,兼容于ARM VPFv3架构,并与前一代的ARM浮点运算协同处理器之间维持软件兼容。完全支持IEEE-754的浮点运算,其执行速度媲美先前的“run-fast” 高速模式,不会出现简化软件的受限例外,并进一步提高 浮点运算程序代码的速度。

此外,系统还加入额外的16位浮点运算数据类型转换指令,增进与嵌入型3D处理器之间的互动,如:ARM Mali 绘图处理器。

Cortex-A9浮点运算平均效能比前一代的ARM浮点运算协同处理器多出一倍以上。一个Cortex-A9 FPU能大幅改善精密绘图、3D、图像处理、以及科学运算解决方案的性能。 |

Cortex-A9 MPE 能搭配Cortex-A9处理器,并提供一个具备Cortex-A9 浮点运算单元的效能与功能的处理引擎,加上由ARM Cortex-A8处理器首次推出的ARM NEON Advanced SIMD 指令集,进一步加快各种媒体与讯号的处理功能。

MPE延伸了Cortex-A9处理器的FPU,提供一个quad-MAC以及额外的64位与128位缓存器,支持为数众多的SIMD运作模式,每个周期能处理8、16、32位整数与32位浮点运算数据。

为进一步强化SIMD功能,MPE亦支持混合数据类型,排除封装/解封装所耗费的资源,以及结构化的加载/储存功能,让数据不必在演算格式与机械格式之间来回转换。

运用MPE亦能增加FPU可使用的缓存器档案容量,并支持32个双倍精准度缓存器,同时保有Cortex-A9处理器的32/64位纯量浮点运算与核心整数运算效能。 |

结论

运用MPE亦能增加FPU可使用的缓存器档案容量,并支持32个双倍精准度缓存器,同时保有Cortex-A9处理器的32/64位纯量浮点运算与核心整数运算效能。

单核心处理器为现有的ARM11等级组件提供更高的效能与省电效率,带来强化的功能与更低的功耗,让行动设计能延长电池续航力。各种实作特性亦带来完全的架构软件兼容性,让业者能以更低的成本达到Cortex-A8等级的效能,使相关软件投资能拓展至市场。

MPCore处理器提供先进的电源管理功能,进一步降低耗电量,并在越来越多的市场与应用中,超越产品对功耗的需求。Cortex-A9 MPCore亦提供前所未有的扩充效能,发展许多以往无法享受ARM处理器省电设计的市场。

经过特别设计的完整支持技术,能整合至Cortex-A9处理器,进一步提升效能,满足各种特殊应用与市场的需求,特别是无线、娱乐、影像、以及其他高阶多媒体应用。