不可或缺的PLD

PLD可编程逻辑元件内含一系列可编程功能元件,利用这些元件的配置和互连可实现基板上特定的硬体管理功能。一般而言,软体设计工具可将某个逻辑功能如基板硬体管理,转换为特定PLD的配置位元流(bit stream),可用于互连和配置可编程功能元件。配置位元流位于可编程逻辑元件内的配置快闪记忆体中。

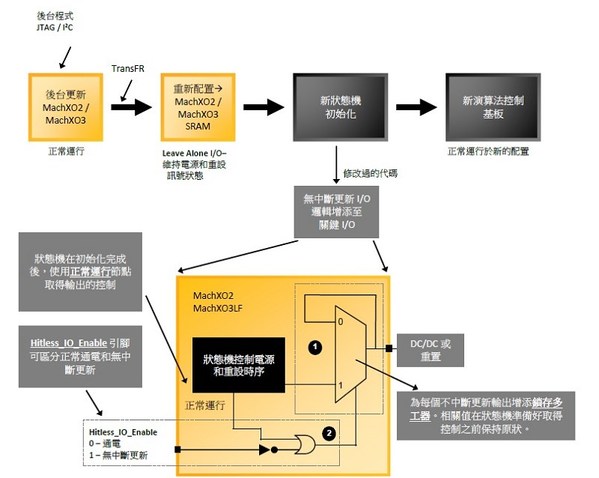

当基板通电后,配置快闪记忆体中的内容将自动传输到晶片内的配置SRAM,使配置可编程功能单元执行所需的硬体管理任务。 PLD更新硬体管理功能时,可透过不同的位元流从后台随时载入到配置快闪记忆体,无需中断可编程逻辑元件执行中的硬体管理功能。将新储存至快闪记忆体的配置传到晶片内的SRAM会造成电源重启,中断系统的正常运行(如图1)。

在配制过程中保持稳定的输出

高常用性系统无法接受因电源重启导致的作业中断。由于可编程逻辑元件的I/O可使基板上主要的ASIC和CPU实现DC-DC转换器和控制重设讯号,但在重组时可编程逻辑元件的输出需保持不变。保持PLD在重组时的输出稳定,为其应用设计带来多项挑战。

莱迪思MachXO2或MachXO3 PLD系列支援多项功能实现系统更新零停机(如图2)。首先,PLD进行「后台更新」透过JTAG、SPI或I2C载入新的配置资料至其配置快闪记忆体,待载入完毕,「TransFR (Transparent Field Reconfiguration, 透明现场重组)」 指令将新的PLD配置从快闪记忆体传输到PLD的配置SRAM,执行「TransFR」指令的同时启动「保持当前状态(Leave Alone)」功能,确保所有的I/O值在传输过程中保持不变,最后,在「逻辑初始化」步骤,状态机将开始重新启动电源管理并重设分配。导致电源中断,强迫基板进行电源重启的过程。

| 图2 : 采用MachXO2/ MachXO3无中断更新I/O 的PLD重组步骤 |

|

使用无中断更新I/O解决问题

为了支援系统更新零停机,PLD元件必须能使新影像所创建的状态机在初始化阶段时,能确保控制电源以及其他逻辑讯号的输出保持不变。新演算法经过初始化之后,即能管控电源和其他逻辑讯号。

为了使得关键I/O在初始化过程中保持原状,使用者设计中需增添「无中断更新I/O」,如图3所示,这需要为每项关键输出增添一个锁存多工器(latch -mux),在状态机初始化的过程中保持输出的最终已知状态,并在初始化过程完成后将输出控制交还至状态机。该电路能运用「Hitless_IO_Enable」输入区分正常(通电)启动和重组状态,可避免在正常的通电过程中发生关键输出I/O值被锁的情况发生。

深入探讨

PLD提供设计便利性和绝佳效能,可管理基板上DC-DC转换器、监测和控制关键讯号、整合串行通讯并执行其他内务管理功能,为高常用性系统理想的硬体管理元件。

图3说明新位置载入至MachXO2/ MachXO3元件配置SRAM时,无中断更新I/O在状态机初始化过程中所发挥的作用。

| 图3 : 无中断更新I/O在初始化期间使关键I/O保持最终已知状态 |

|

为每项输出增添一个锁存多工器,只要多工器的控制输入为「0」,输出就能保持现值不变。这意味着无论状态机的输出状态如何,DC-DC转换器可保持「on」(如果先前处于「on」的状态)。当控制讯号为逻辑值「1」时,DC-DC转换器的状态则由状态机控制。状态机透过「正常运行」节点控制多工器输出。晶片最新添加的「Hitless_IO_Enable」输入可区分正常的「通电」配置(状态机初始化过程中DC-DC转换器输出受到控制)和无中断重组流程(状态机初始化过程中DC-DC转换器保持不变)。

假设控制无中断更新流程的「Hitless_IO_Enable」讯号设为「1」。

在初始化前,状态机将「正常运行」讯号重设为「0」。锁存多工器将忽略来自状态机的输出,并且DC-DC转换器的「Enable」讯号保持不变。

当PLD的逻辑准备好恢复正常运行时,将「正常运行」讯号设为逻辑值「1」(高电频),允许其取得DC-DC转换器的控制。此时基板的DC-DC转换器和重启将由复原的电源和重设控制状态机控制。

实际案例

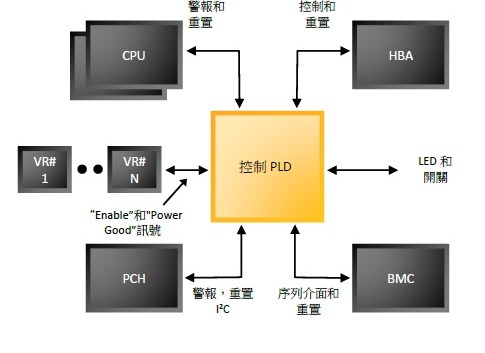

图4说明PLD在供电、监控和管理CPU丛集(cluster) 以及平台控制中心(Platform Controller Hub, PCH)、基板管理控制器(Baseboard Management Controller, BMC) 和主机汇流排转换器(Host Bus Adapter, HBA ) 等基板级子系统的使用情景。

在此例中,PLD主要负责基板负载点电压调节器(Voltage Regulator, VR) 的上电和断电时序,并在电源重启时将重设和控制讯号保持最佳的状态。在正常运行时,PLD监控子系统的温度、电压、记忆体和I/O故障等警报参数或状态变化,同时将控制讯号稳定保持在合适的状态。

| 图4 : 将机架式服器的控制/内务处理功能整合至PLD |

|

BMC在后台更新伺服器的控制PLD并启动「TransFR」指令以便用更新的配置运行PLD。若没有无中断更新I/O的情况下,控制和重设讯号或是 VR讯号将不能在初始化过程中保持不变。例如,若CPU或其外设上的重设讯号在重组过程中发生变化,无论当下CPU执行何种功能都将进行重新初始化并开始重启流程。

同样的,如果「Power Enable」讯号发生变化,VR或负载点的电源供应将中断,导致由该VR供电的元件进入未知状态,造成基板运行中止、遗失或扰乱资料,甚至对基板的电子元件造成物理损害。

为关键讯号增添无中断更新I/O机制可使PLD在重组的过程中暂停外部感测和控制讯号。因此,伺服器的关键功能在PLD的常态性维护和升级过程中不受中断。此功能也有益于产品开发,能够缩短除错时间或是在安装机架时建构专用产品的变数。

总结

PLD为灵活、高成本效益的解决方案,可控制DC转换器、桥接I/O通道以及执行复杂电子系统中的其他基板级硬体管理功能。元件支援现场升级,可为制造商提供运行中变更配置所需的灵活性,实现设计错误更正或是为产品添加新功能。

随着无中断更新I/O架构的面世,PLD现可以无差错、有保证的方式进行重组。其设计中的闸道数量的增加通常少于1%,并且无需外部元件即可执行。无需电源重启即可实现稳定可靠的配置变更,无中断更新逻辑使CPLD成为网路、资料中心储存设备以及其他任务导向应用中硬体管理解决方案的理想选择。

(本文作者为莱迪思半导体资深产品行销经理)