封裝是屬於半導體產業的後段製程,其景氣循環約落後晶圓製造一至二月,且市場與半導體景氣息息相關。(表一)為半導體市場產值的預估值,估計從1999年至2002年間,半導體市場將維持15﹪以上的成長。(表二)為封裝市場的預估產值,在1999年至2003年間,其中DIP、CC與PGA是呈現負成長,而SO與QFP則維持緩慢的成長;但值得特別注意的是BGA與CSP的市場,其中BGA的複合成長率為16.1%,CSP為48.9%。

從這裏我們可以看出整個封裝型態改變的趨勢,傳統式的封裝不再獨佔市場,屬於先進製程的BGA與CSP已成為市場新主流。造成BGA與CSP迅速成長的原因為何?我們近年來IC產品的走向朝著以下的趨勢發展:1.輕、薄、短、小;2.高I/O數;3.良好的電性與散熱要求。所以我們不難了解BGA與CSP的快速成長乃是其符合市場的需求。

另外,Flip Chip開發至今雖已有30年以上,但由於其專利期限已過,故目前為封裝廠相繼研發的重點,而成為高階封裝的主流之一。本文將以高階封裝市場為主題來探討PBGA、CSP與Flip Chip的現況與發展。

高階封裝市場概況

PBGA市場概況

PBGA封裝為目前高腳數封裝之主流,已廣泛地應用在晶片組IC(Chipset)、LCD Panel控制IC、繪圖晶片與高階交換器IC。傳統的導線架封裝,受到間距(Pitch)的極限限制,其出腳數被限制於256腳以下,故腳數超過300腳以上之IC多以PBGA為最佳選擇,同時PBGA也被證實較QFP有更佳之電性與散熱特性,對於高速運轉之IC所產生的高熱有很好的散熱效果。

目前市場上的規格已標準化,常見的規格有27x27、35x35、37.5x37.5與40x40。其中27x27應用於LCDPanel控制IC及網路交換器IC,35x35與37.5x37.5鎖定於晶片組市場,而40x40則用於高階處理器(如Layer-3網路交換器晶片)。

由於SOC(系統單晶片)及多晶片模組(MCM)的概念興起,IC的功能越來越多,也越複雜;併隨而來的就是更多的I/O數與更嚴格的散熱要求,這都是PBGA市場逐漸成長的原因(表三)。

CSP市場概況

近年來拜快速成長的行動電話、可攜型個人數位助理(PDA)與筆記型電腦之賜,促成了CSP(Chip-Scale Package)封裝市場的快速掘起。所謂CSP一般的定義為:1.封裝產品的長度及寬度<1.2倍晶片的長度與寬度;2.封裝產品的面積<1.5倍晶片的面積。該封裝方法使得單位面積內達到更高的腳數,滿足了輕薄短小的要求,由於此種特性,造就了其為記憶體晶片市場上的主流地位。

此外,藉由晶片的堆疊技術,在一顆成品內整合3種晶片絕非難事,如此大幅節省廠商生產成本與IC所佔空間,如Flash Combo便是一例。目前全世界發展CSP的封裝方式超過40種以上,無法以單一的封裝方式作為整個的代表。

(表四)將CSP分為四大類型,其中BGA CSP(Fine-Pitch BGA,或Mini BGA)之材料成本逐漸下降,而使其成為CSP市場上的主流。同樣歸為CSP的μBGA一直存在著兩個重要的問題,其一是居高不下的成本,其二是Socket規格不統一的問題。

隨著晶片大小的不同而會造成封裝成品大小的不同,這會造成Socket選擇的複雜性或增加廠商的模製具投資成本;故缺乏標準化的封裝成品為其主要的缺點。此外IC設計者應有很高的自由度來改變晶片的大小(例如改以0.18微米設計取代原先之0.25微米),以降低成本,但卻不能因成品的大小一再改變而增加其顧客在PCB設計(Layout)上的困擾。

至於來勢沖沖的Flip Chip在CSP市場中也遭遇到居高不下的成本與缺乏標準的Socket問題,使得其市場一直裹足不前;所以Flip Chip便將其主戰場移至更高腳數或對於散熱有高度要求的產品中。

CSP的應用方面以追求輕薄短小的產品居多,尤以行動電話及可攜式電子產品之記憶體為最。在記憶體方面廣泛地應用在Flash、Low PowerSRAM、Flash Combo、DRAM及RambusDRAM。而未來高頻的DDR DRAM推出,因其更強調封裝的電器特性,故可望採用BGA的封裝方式,BGA CSP最有可能因成本優勢成為最佳選擇。

Flip Chip市場概況

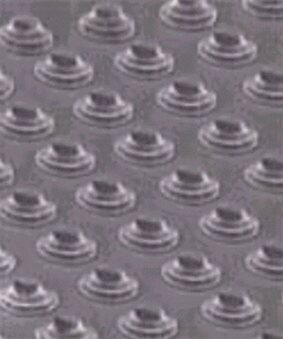

Flip Chip的封裝方式不同於目前的打線方式,是以錫鉛凸塊(Solder Bumps)或金凸塊(Gold Studs)直接生長在晶圓表面之後,再將晶片正面朝下直接使晶片上的pad與基板(substrate)結合的技術。如此一來縮短了晶片與基板間的距離,加快了訊號傳輸的速率。由於晶片背面不需加Molding,除了使元件更輕外,也提高了散熱效果(圖一)。

| 《圖一 Bumping at Flip Chip》 |

|

另一與打線技術不同之處,在於基板與晶片間的填充(Underfilling)製程。它除了具備足夠的接合性與防止可能的污染物之外,更要能抵抗在做接合時因熱膨脹(CTE;Coefficient of Thermal Expansion)所發生的不一致縮脹(Mismatch)與減低凸塊所產生的應力,此點對廠商來說是很難克服的一道障礙。

當晶片的I/O數增加的同時,以四周出點方式有時已無法符合設計上的需求,故設計者會將I/O分佈至全區域或部份區域,這時就不能利用打線方式來進行封裝,Flip Chip是唯一選擇。此外,Flip Chip被大量採用在電腦用的高階CPU封裝,因該產品對於散熱有嚴格的要求。

高階封裝市場的未來發展

由於PBGA、CSP與Flip Chip目前技術多已成熟且廣泛地應用在各類產品上,但基於產品的特性與需求各異,而使不同技術在不同產品市場中的發展也有所差異,故以下將市場分為低腳數與高腳數市場,更可清楚的看出此三種封裝的市場定位及發展(表五)。

低腳數市場

相同的晶片使用TSOP或SO封裝,其成品面積約為使用CSP封裝之6至8倍,在面對輕薄短小的趨勢下,TSOP與SO已無法滿足小體積的要求。就行動電話的記憶體來說,即使是多1mm的差異就不能被放入成品基板之中了,故CSP取代了TSOP與SO在低腳數市場的地位。

但是CSP的種類甚多,要採用BGA CSP、μBGA抑或Flip Chip?就前面所提,μBGA雖然能將產品封到接近晶片大小,然而BGA CSP也很容易做到,且少了很多μBGA存在的問題,這也是μBGA一直未起來的原因。Flip Chip由於其產業結構(Infrastructure)並未成熟,故其成本無法有效地降低,除此之外,它還有其他技術上的問題。

表面黏著設備相容性

在封裝成品與PCB的黏合製程中,BGA可使用相同的SMT設備而不需要變更其它製程,但Flip Chip在經過SMT之後還要加上另一樣填充(Underfilling)的製程,這樣一來提高Flip Chip在SMT製程中的不穩定性與複雜性。

重工性

在SMT過程中,無可避免的會發生重工的情形,故產品被要求有很高的重工性(Reworkablility),以BGA 而言,使用標準的SMT設備即可以進行重工,但Flip Chip一旦經過填充製程後,就不太可能重工了。

可測試性(Testability)

通常Flip Chip (此指COB;Chip on Board)一旦上了SMT之後就無法進行測試,在無法得知晶片的電性之下,大大地提高了廠商的風險。BGA在封裝完成後即可交由測試廠進行測試。

由上可知BGA CSP佔盡了優勢,而市場上的趨勢也顯示著BGA CSP正迅速地成長並成為CSP的霸主。

高腳數市場

目前在超過100腳至256腳間的產品多數仍採用QFP,但以低成本為號召的QFP正因BGA的成本逐漸下降而受到嚴重的挑戰。在數年前每隻腳平均價格BGA約為QFP之兩倍,如今在100腳至208腳的封裝中,BGA的價格幾乎與QFP一致。BGA已有逐漸取代QFP之趨向。在超過256至600腳間仍以BGA為主流。另在特殊應用市場,如更高腳數(1000腳以上)或高散熱需求產品,還是以Flip Chip為最佳選擇。

由以上的分析中可看出,未來幾年內,在低腳數市場BGA CSP將仍維持其主流地位;而在高腳數的封裝市場中,則是BGA與Flip Chip的互爭高下,如有興趣,歡迎至www.neopac.com.tw查詢。(本文作者目前任職於訊捷半導體)