什麼是當今最吸引人們注意的流行先進技術?相信以下的專業用詞都經常出現在周遭與新聞、文章之中,如人工智慧(Artificial Intelligence)、深度學習(Deep Learning)、雲端計算(Cloud Computing)、超級電腦(Supercomputer)、自動駕駛等。

包括Google、Amazon、Intel、Nvidia或是AMD等,從這些世界級技術巨型企業的策略中可以發現,不約而同的都正積極投下巨額資金,來開發前述的這些軟硬體技術和相關的應用。

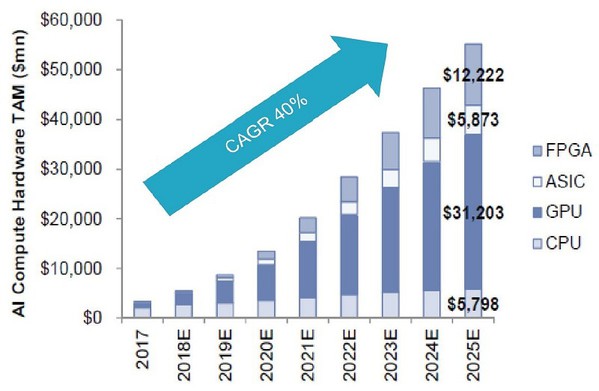

高盛集團對於人工智慧在未來幾年發展的研究顯示,組成人工智慧機能應用所需要的硬體,例如特殊應用IC(ASIC)、繪圖處理晶片(GPU)、中央處理器(CPU)、場域可程式化閘陣列(FPGA)等元件,在未來數年間的全球市場規模,將會以40%年平均成長率急速擴大(圖一)。

| 圖一 : AI運算硬體元件的世界規模成長預估。(source:Goldman Sachs 2018) |

|

晶片封裝高度整合的關鍵:異質整合技術

由於演算法、大數據和高效能微晶片的進步,是扮演推動這一新世代科技浪潮的最大動力。因此隨著終端電子產品快速發展,智慧型手機、平板電腦與穿戴裝置等產品不斷朝輕薄短小、多功能、高效能、低成本、低功耗,及小面積等要求發展的情況下,需將把多種不同功能的晶片整合於單一模組中。因此,包括晶圓代工廠、IC設計公司等IC製造業者,相繼投入先進封裝技術領域。根據Yole資料顯示,2017~2021年全球先進封裝規模從250億美元增至310億美元,年複合成長率約7%。

而這些先進技術的應用與能力,都在近幾年內取得了令人驚訝的巨大進展,然而在這些看似不同領域技術或科學的背後,都有一個共同的特點,那就是都採用了異質整合(Heterogeneous Integration)的積體電路設計。

例如,近來出現了另一種稱為「chiplet(小晶片)」的設計概念。所謂chiplet,就是具備特殊用途或單一功能的KGD(known good die)或IP區塊;然後,在開發高效能系統時,透過搭配選用適當chiplet的堆疊累積,來達成所需的系統效能。目前的封裝技術是以並排的方式朝2.5D技術發展,透過中介層(interposer)和重分布層(RDL)設計來進行整合。而3D封裝則是把多顆晶片向上堆疊,除了底層晶片之外,所有晶片都需要透過TSV (矽穿孔)來傳遞訊號。

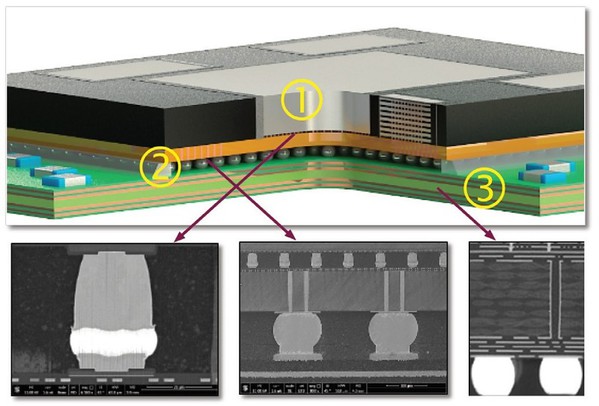

| 圖二 : 2.5D封裝的3個主要特色結構:1. 將HBM和SerDes微晶片使用微凸塊整合到中介層、2. 矽通孔(TSV)中介層連接到C4或大型CuP、3. 封裝載板。(source:AMKOR) |

|

英特爾(Intel)在CES 2019主題演講中,發表了首款採用3D封裝技術的處理器(Lakefield),引起眾人的注目,也讓3D異整合質封裝正式邁入商品化的程度。Intel利用堆疊設計,整合各式晶片、I/O、結構等,進而提升晶片設計的靈活性,也大幅減少多核處理器所需的晶片空間,讓體積縮小到僅有12mm×12mm。

透過新世代的封裝技術突破摩爾定律

根據2018年所發表的IRDS Roadmap(International Roadmap for Devices and Systems),到2030年半導體製程技術將達到1.5 nm。但是在半導體前段製程中,根據摩爾定律應該在5nm左右就難以再突破了,但是隨著技術進步到28nm之後,成本反而會逐漸下降。這似乎違背了產業中的基礎常識。

例如台積電(TSMC)不斷地將元件的製程持續縮小,從14 nm、10 nm、7 nm甚至於目前最新開發的3nm,不僅僅提升CMOS元件的運作速度,同時也大幅度增加了邏輯閘數。雖然目前3nm製程技術仍在早期研發階段,台積電也沒有發表例如效能及功耗指標等等任何技術細節(如,和5nm製程相較能提升多少效能),只描述3nm將會是一個全新的製程技術,所以必然也會有新的架構、技術、材料等。而不是5nm製程的提升。

這相當於每經過18-24個月的時間,可以在同一空間中,讓元件數增加一倍,除了加快晶片本身的運作速度外,還有兩個因素變得越來越重要。

一個是採用高頻寬記憶體(HBM;High Bandwidth Memory)的架構,不僅可提高計算能力之外,還可以降低系統總功耗和增加記憶體的頻寬;另一個則為了達到高速資料收發的序列化或解序列化(serializer/deserializer),也就是SerDes。SerDes IO的模組可以整合到主晶片中,也可以作為單獨的晶片生產製造。

而要如何將這些高速性能進行整合?其中一個關鍵點,就是讓先進的2.5D異質整合結構晶片封裝技術來扮演這個角色。但是為什麼需要採用2.5D封裝技術,以目前來說,2.5D封裝是一種高階的IC封裝技術,可實現各種IC的高速整合。

縮短元件之間的距離,就能夠加快處理速度

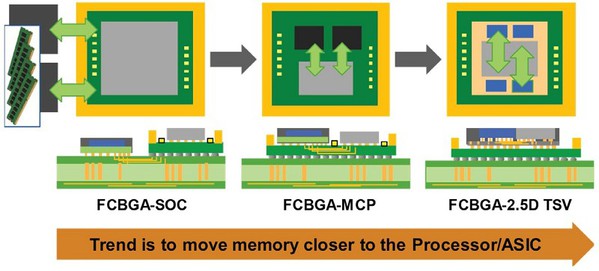

研發這種複雜的封裝結構有多種原因。如圖三所示,為了滿足更高速的處理速度需求,DRAM記憶體在物理性結構上必須更接近CPU。因此結構上讓每個元件都是獨立的,並安裝在載板(印刷電路板或PCB)上,為了能滿足更多高性能應用,基本上都是採用系統級封裝(SiP)技術。

| 圖三 : 先進的封裝發展趨勢。(source:AMKOR) |

|

在這樣的封裝方式上,便可以將記憶體和主要CPU元件在載板上連接,來形成FCBGA的結構,然後再轉移至2.5D封裝上。透過使用新一代的HBM DRAM,可以將邏輯和HBM直接連接到矽中介層,兩個IC之間的最小距離已經可以達到小於100μm。

由於縮短元件之間的距離,就能夠降低訊號延遲,提高了電子訊號的品質,而達到了更快的處理速度,和更低的能耗。

另一個原因是,使用超出DDR4或GDDR5 / GDDR5X / GDDR6的矽中介層方法可以實現極高的HBM數據頻寬。HBM使用1024 Bit,這樣可以達到比DDR4和GDDR所能提供寬廣得多的並列式匯流排。

這是因為HBM和HBM2具有大約4,000個I/O和電源連接,所以需要非常高的佈線密度來連接到主晶片。由於傳統FCBGA載板線寬的限制,是無法滿足這種高密度連接的要求,而2.5D矽中介層連接就必須從FCBGA轉移到矽晶片。

還有一個重要趨勢是用於高速數據傳輸的SerDes。單通道(Single Channel)SerDes可以達到每秒10 Gbps、28 Gbps、56 bps甚至高達112 Gbps。

在高速數據中心應用中,主晶片能夠控制多個SerDes通道。隨著主要CPU和GPU製造技術的進步,發展SerDes的設計公司已經開始開發新一代生產製程IP,提供晶片業者可以將其整合到主晶片的設計之中。但是,面對高速和高性能的要求相當高時,SerDes驅動卻不能滿足Time to Market、更新的矽晶節點,以及驗證新SerDes IP的成本。

對於某些應用,卻可以透過利用2.5D異質整合的封裝解決方案,在封裝等級上整合主要晶片以及多個SerDes晶片。

另一個考慮因素,是量產時的良率。理論上,單一晶片的表面積越大,良品率就越差。因為根據玻色-愛因斯坦(BOSE-EINSTEIN)良率模型,兩者之間是存在巨大差異。Y = 1 /(1 + AD)^ k(Y為成率,A為晶片面積,D為缺陷密度,k為難度係數)。對於需要做到大面積的產品這一點,可以預期其良率是相當的低。不過如果是透過使用2.5D異質整合封裝的技術,將所需區域分成多個小晶片,就可以提高產量的良率和大幅降低成本。

各種大型晶片都可以透過異質整合技術來完成

高速微晶片大多依賴TSV矽中介層技術來進行高密度佈線,主要原因是帶有TSV的中介層可以支援2μm/2μm以下的再分布層(RDL)和40μm的微凸塊。這是FCBGA載板密度的10倍,因此可以縮短連接距離,並產生更好品質的電子訊號,而實現異質整合晶片架構。

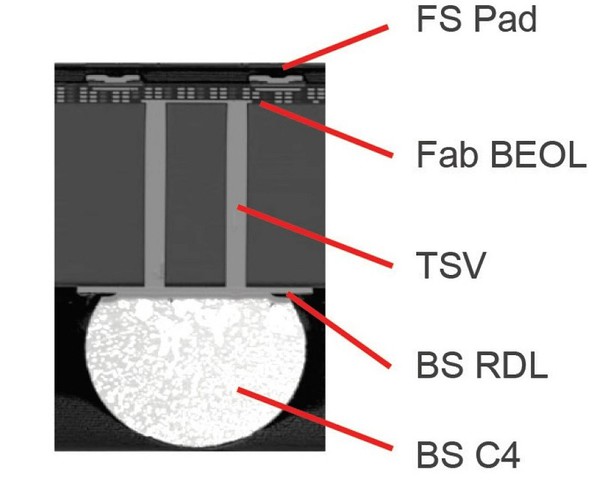

例如Amkor的TSV矽中介層使用晶圓級製造技術,這樣的技術是源自於晶圓代工廠所製成的300mm TSV晶圓,接下來再對背面和錫鉛凸塊的保護層,進行蝕刻和薄化已經填充的TSV,最後再完成單片化。此過程通常稱為產線中段(MEOL;mid-end-of-line)製程。主要的製作過程是形成將上層微型凸塊連接板,到下層FCBGA載板連接錫鉛凸塊的橫截面。如圖四所示。

| 圖四 : 從前(FS)PAD到後(BS)C4的封裝剖面。(source:AMKOR) |

|

在Chip on Substrate製造過程中,矽中介層首先連接到載板,然後將多個微晶片連接到中介層以形成異質整合封裝結構,這種設計稱為RDL First或Die Last。因為RDL在製造過程中會首先完成,然後將晶片連接到RDL中介層。

這種設計的優點是可以在中間進行測試,標記出有缺陷的中介層和未完成的產品,這樣就不會在後續的封裝製程中使用到這些不良品,也不會浪費寶貴的晶片。因此可以達到增加產能的目標,以及提高良率。

Chip on Wafer(CoW)封裝是Chip on Substrate的下一代技術,使用矽晶圓作為載板進行晶圓級封裝。與CoS技術的觀念不同的是,CoW是將晶片連接到中介層,最後連接到覆晶(Flap Chip)的載板。Chip on Wafer封裝技術具有非常好的物理結構優勢,適用於更大的晶片及較大的中介層。

HDFO封裝是不使用TSV技術的晶圓級封裝中的下一代Integrated FCBGA技術。為了實現此一目標,是利用微凸塊‧錫鉛凸塊,連接將微晶片連接到多層細微的RDL和BGA,而達到半成品的程度,最後再連接到FCBGA載板以形成異質整合封裝。這樣一來就可以達到高佈線密度,和良好的電子訊號品質,並且不須要進行TSV處理,來更進一步地降低成本。

HDFO異質整合封裝,並非只可用來生產GPU和FPGA,而是對於包括網路和伺服器等等應用所需的大型晶片,都可以透過異質整合封裝的技術來完成。