隨著首批商用5G無線網路陸續啟用,愛美科為5G及未來世代通訊應用準備了下世代的行動手持裝置。更確切的說,該團隊正在研究如何運用與CMOS製程相容的三五族材料技術來改良前端模組。這些前端模組將以毫米波運作,尺寸精巧、性能強大且具備成本及能耗方面的效率。愛美科的計畫主持人Nadine Collaert將於本文說明愛美科目前正在研發的相關技術,並展示第一批功能元件。

5G帶給行動手持裝置新的挑戰

第五代行動通訊網路應該會將物聯網推升至更高境界。5G將實現超級行動大寬頻、低延遲,以及超過100Gbps的資料傳輸率。藉著上述特性,5G將鞏固下一代科技的基礎,從自駕車、機聯網(machine-to-machine communication;M2M)到智慧城市和人工智慧。

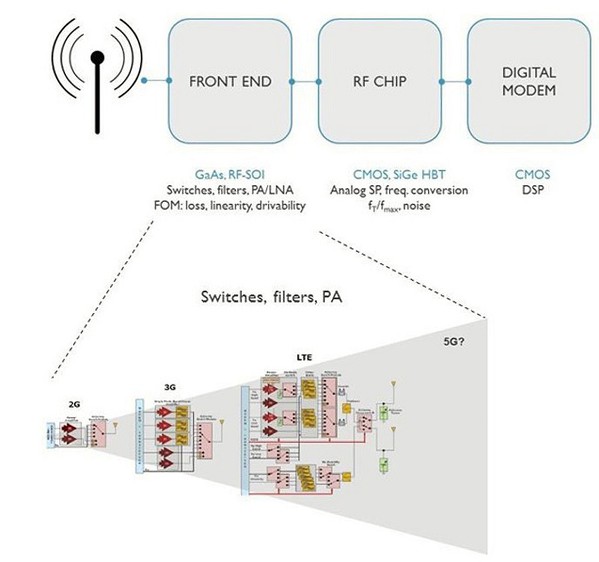

2019年,我們看到首批商用5G無線網路陸續啟用。在5G部署的第一階段,無線通訊主要由sub-6 GHz射頻頻段支援。然而,這些頻段中的頻譜供不應求,這就驅動操作頻率逐漸朝向毫米波運作,28-39GHz的頻段則是下一步。採用這些毫米波頻段將對5G的整體網路基礎設施產生重大影響,包括基地台、小型基地站和用戶設備。對行動手持裝置(例如智慧型手機)來說,這個重大影響就變成日趨複雜的前端模組。前端模組運用功率放大器、射頻開關和濾波器作為主要構件,接收來自天線的訊號或發送訊號至天線。

| 圖一 : 各代行動通訊射頻前端模組設計趨向複雜化的示意圖 |

|

為了讓射頻前端模組能以毫米波運作,就必須結合高速及高輸出功率。此外,將這些模組用在以電池供電的手持裝置上,對其規格尺寸、成本和功耗效率帶來高要求。這些需求特別會影響到未來射頻前端模組的發射端。

目前這類模組由各種技術構成,包括基於砷化鎵(GaAs)且高速的異質接面雙極電晶體(heterojunction bipolar transistor;HBT)—通常在小型且高價的GaAs基板上製造,用來製造功率放大器;以及射頻絕緣體上矽(RF-silicon-on-insulator;RF-SOI),用來製造射頻開關。這些元件各自分別製造及封裝,隨後在同一片載波基板上組裝。創新的解決方案必須要微縮晶片尺寸和降低成本,並提高傳輸速度和功率輸出。

關鍵解方:共整合(co-integration)

實現微縮尺寸和降低成本的一種誘人辦法,就是將射頻前端的輔助元件以一種相容於Si-CMOS製程的技術共整合。這些元件最終會和無線電通訊晶片的其他元件(像是控制電路、ADC或DAC)共整合。除了成本和尺寸優化外,共整合應該還會提升整體電路的能源效率。

2018年初,愛美科成立了「產業聯盟計畫(Industrial Affiliation Program;IAP)」,以實現上述目標。在計畫第一階段,一項與CMOS製程相容的III-V-on-Si技術正在開發中,用以製造具備高輸出功率的高速元件。

在計畫第二階段,愛美科的團隊會探究將這些高速元件共整合至其他基於CMOS製程元件的可能性,看是運用單片或2D整合(將矽元件和三五族元件放在同一片基板上),或是利用2.5D或3D整合技術。

確認理想元件

愛美科團隊正在研究哪一種(和CMOS製程相容的)元件和結構能夠實現預期的性能特性。兩種途徑正在開發中,各自允許不同的操作頻段運行。

第一種途徑是測試基於氮化鎵(GaN)的元件,提供較低頻的毫米波運作。基於三五族寬能隙材料的元件具備處理高功率的能力,因此很有希望被用來製造具高輸出功率的功率放大器。這些元件目前用於電力電子應用,也用在基地台—通常以超過28V的工作電壓運作。為了應用在行動手持裝置上,工作電壓必須大幅降低(至5V以下),且緩衝層必須與射頻相容,將射頻訊號損失最小化。

其他設計挑戰包含將元件整合至矽,以及找出能夠傳輸高速射頻工作速度的合適架構。為了協助達成這個目標,愛美科的研究團隊可以憑靠本身在GaN-on-Si技術上長久累積的專業—該技術原本用於發展電力電子應用。

第二種途徑聚焦在將基於磷化銦(InP)的元件整合至矽,因而得以借助愛美科在III-V-on-300mm Si技術上的專業—該技術發展背景是為了實現CMOS製程中的尺寸微縮。

首先,該團隊正在研究HBT元件,這是一種射極區與基極區採用不同材料的雙極性電晶體(bipolar junction transistor;BJT),因而形成異質接面。射極包含磷化銦鎵(InGaP)且基於GaAs的HBT元件已顯現出高速能力。而高電子遷移率可望出現在基於砷化鎵銦(InGaAs)或基於InP的元件上,為使用遠超過28-39GHz的毫米波操作頻段鋪路,並解決6G所會面臨的挑戰。

比較GaN-on-Si元件結構 以實現高頻操作

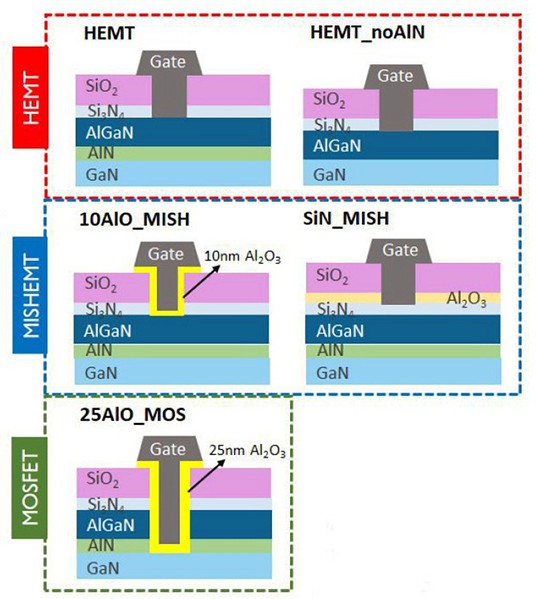

作為第一種途徑,愛美科研究員使用標準矽CMOS工具中的無金加工,將基於GaN的元件和氮化鋁鎵(AlGaN)阻障層整合在200mm的矽晶圓上。為了確認出高頻操作應用中最具前景的可微縮結構,該研究團隊比較了三種不同的元件結構。他們在尋找同時具有正臨界電壓(threshold voltage;VT)及負臨界電壓的元件,以確保設計電路的彈性。

性能表現優異的元件都是基於GaN的高電子遷移率電晶體(high electron mobility transistor;HEMT)元件。這些元件是採用蕭基金屬閘極(不含高介電氧化物)且具備負臨界電壓的空乏模式(depletion mode;d-mode)元件,或稱常開型元件。

在這個性能測試「頻譜」的彼端,是基於GaN的MOSFET常閉型元件,具備正臨界電壓。該正臨界電壓操作模式的代價是性能,因為AlGaN阻障層在閘極堆疊沉積前就在通道區被蝕刻移除,導致高遷移率的二維電子氣(two-dimensional electron gas;2DEG)被移除。

而性能表現介於HEMT和MOSFET元件的是金屬絕緣半導體HEMT(metal insulator semiconductor HEMT;MISHEMT)元件或金屬氧化物半導體HEMT(metal oxide semiconductor HEMT;MOSHEMT)元件,這些元件結合HEMT和MOSFET各自的優點。可以想見透過優化AlGaN阻障層的厚度,這些元件的臨界電壓能在正負值之間調適至最佳狀態。

| 圖二 : 基於GaN的元件架構類型:HEMT、MISHEMT和MOSFET。 |

|

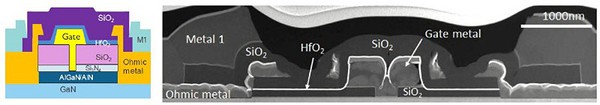

| 圖三 : 加工完成後的元件橫剖面示意圖與穿透式電子顯微鏡影像。 |

|

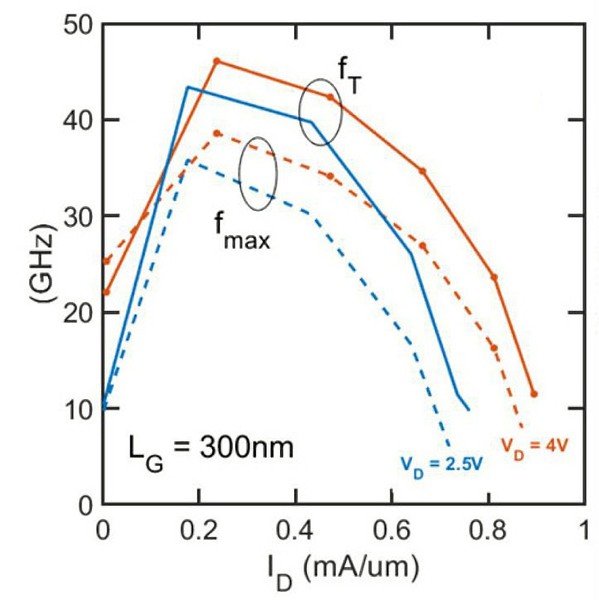

愛美科的研究團隊表示,就高頻操作而言,MISHEMT元件在尺寸擴充性和雜訊性能方面勝過其他元件類型。這些MISHEMT元件也展現了最高的遷移率,亦即場效載子遷移率大於2000cm2/V.s。閘極長度為300nm且汲極偏壓只有4V的情況下,可獲得fT/fmax的尖峰截止頻率。fT/fmax用以測量元件的固有速度,而MISHEMT測得的上述數值能確保以sub-6 GHz頻段運作。

| 圖四 : 堆疊於 200mm 矽晶圓上的GaN/AlGaN元件:在VDS=2.5V及4V的情況下,電流增益(currant gain;fT)和單向功率增益(unilateral power gain;fmax)所測得的截止頻率。 |

|

為了實現更高的操作頻率而優化元件,就必須進一步微縮元件的閘極長度,因為這將有助於獲得更高的fT/fmax將氮化鋁銦(AlInN)作為阻障層材料的第一批測試結果顯示,透過增強2DEG特性,元件性能可能得以進一步提升,因而提高基於GaN的MISHEMT元件的操作頻率。

矽上首款基於GaAs的HBT功能元件:新的成長方法

應用日益增長的三五族材料(例如GaAs on Si)通常伴隨著缺點—主要是螺紋狀差排(threading dislocation),原因是不同材料間的晶格嚴重不匹配。這些缺點導致漏電流,會明顯拉低元件性能。

降低缺陷密度的一個辦法是透過製造深厚(1-10μm)且應力鬆弛的緩衝層,舉例而言,矽鍺(SiGe)或複合三五族變晶堆疊。如此,緩衝層上就會生成三五族的主動層。

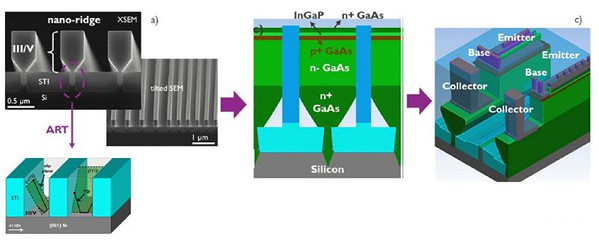

愛美科提出一個不需額外加厚緩衝層的方法。新製程結合了深寬比捕捉(aspect ratio trapping;ART)和材料成長(material overgrowth)技術,這也被稱作愛美科獨特的奈米摺狀結構工程(nano-ridge engineering;NRE)處理。

利用ART技術,一道溝槽會生成在矽基板上,隨後被三五族材料填滿。因晶格不匹配所產生的大多數缺陷,就會被侷限在這個高深寬比的溝槽底部。這確保了窄溝槽外的材料生成的螺紋狀差排密度低。同時,這樣的材料成長讓奈米摺狀結構得以加寬,因而生成大型盒型的形狀。這種材料具備低度缺陷,就可以用來製造元件堆疊。

| 圖五 : 利用NRE方法進行300mm矽晶圓上混合三五族CMOS整合:(a)奈米溝槽生成;缺陷被捕獲在窄溝槽區;(b)利用NRE技術生成HBT堆疊;(c)HBT元件整合的佈局類型。 |

|

藉由這個方法,愛美科近期已展示出首款基於GaAs的HBT功能元件,該元件在300mm矽晶圓上製造,並在邁向實現基於InGaAs的元件發展路上,作為第一塊跳板。

基於GaAs的奈米摺狀結構表面的線差排密度顯示為低於3x106cm-2。至於生成於GaAs基板上的各個階層,其層介面(layer interface)的品質相似。基於GaAs/InGaP的HBT元件隨後製造。這些元件的性能表現優於參考元件,後者在矽基板上加上一層深厚且應力鬆弛的緩衝層。

這項展示顯現出將混合三五族CMOS技術應用在5G和毫米波應用的潛能。為了達到更高的工作速度,愛美科認為下一步是朝向高遷移率且基於InP的HBT元件發展。

![圖六 : 比較本文製造的元件與具有應力鬆弛緩衝層的參考元件[1],圖為兩者的電氣特性差異(gummel plot特性曲線圖)。](/art/2020/02/101324429830/p6S.JPG)

| 圖六 : 比較本文製造的元件與具有應力鬆弛緩衝層的參考元件[1],圖為兩者的電氣特性差異(gummel plot特性曲線圖)。 |

|

總結

下一代5G行動手持裝置需要尺寸小、成本及能耗有效率的前端模組,這些模組相較於第一代前端,要能以更高速運作,並傳遞更高輸出功率。愛美科認為,異質三五族Si-CMOS技術是進步的方法,最終將使得無線電晶片上的其他元件得以共整合。

兩種途徑正在開發中:(一)提供低頻毫米波頻段之用的GaN-on-Si,與(二)用於操作頻率超過100GHz且基於InP的HBTs-on-Si。愛美科已展示了這兩項技術的首款功能元件,以及進一步增強操作頻率的確定方法。這為5G行動手持裝置應用及往後的發展,提供了下一代射頻前端的發展條件。目前開發出的技術將有助於其他也需要高資料傳輸率的應用,像是虛擬實境(VR)或擴增實境(AR)。

(本文由愛美科授權刊登;作者Nadine Collaert為愛美科高速類比/射頻計畫的計畫主持人;編譯/吳雅婷)

**刊頭圖(source:dficlub.org)

參考資料

[1] C. Heidelberger et al., Journal of Applied Physics 123, 161532 (2018).