I/O频宽的需求每三年就会倍增,因此PCIe 5.0是一个早该推出的规范。而在PCI-SIG的努力下,PCIe 5.0规范终于在今年5月正式推出,并且已经有多个设计导入,终端产品预计在2020年就能够陆续推出。

| 图一 : 依据市场的发展,I/O频宽的需求每三年就会倍增。(source/PCI-SIG) |

|

PCIe 3.0的时代,真的令人感觉漫长。甚至一度让人以为那就是「固定」的规格了。然而,那其实是一个诸多纠结的总和。 SSD市场仍不上不下,智慧手机突然抢了PC的风采,网路也还没有很快,一切的种种,造成了PCIe 3.0可以存在的相安无事。

只不过产业变革有时就像海啸,一道大浪打过来,原有陈旧的一切,就会被冲击毁去。而那个大浪,就是目前仍在全速前进的数位转型趋势,它驱动了半导体技术持续突破、让行动网路从4G转进5G、让大数据与人工智慧成为现实。

而这一切都需要更高的运算速度与传输性能才得以实现,因此作为I/O传输的枢纽,PCIe 3.0介面也不得不着手进行升级。

追赶延误的进度 PCIe 5.0加速推出

只不过因为之前的升级作业搁置太久,整整停滞了将近十年,要再重启就立即面临人事全非的窘境,许多的文件与流程都需要重新拟定,因此这个新标准制定的进度就显落后产业许多,同时也出现了需要连升两级的怪现象。

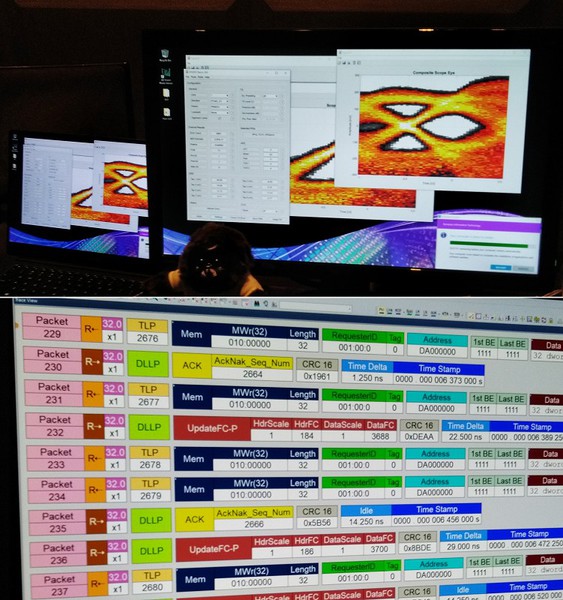

| 图二 : PCIe 5.0的测试与验证方案目前已问世,能支援最前端应用开发。(摄影/篮贯铭) |

|

也就是在PCIe 4.0推出后,不到2年的时间,PCIe 5.0规范马上就出台。但是PCI-SIG副总裁暨开发者会议主席Richard Solomon却说:「事实上,PCIe 5.0是来迟了。」

因为依据市场的发展,I/O频宽的需求每三年就会倍增,因此PCIe 5.0是一个早该推出的规范,目前PCI-SIG的工作就是在补进度罢了。而在PCI-SIG的努力下,PCIe 5.0规范终于在今年5月正式推出,并且已经有多个设计导入(design-in),终端产品预计在2020年就能够陆续推出。

相较于PCIe 4.0,PCIe 5.0在效能上又成长一倍,其信号速率达到32 GT/s,单道的频宽提升至32 GB/2,而x16的频宽则增加到了128GB/s,并维持向下相容(支援4.0~1.0)的功能。除了频宽倍之外,PCIe 5.0也改善了电子的设计,以提高信号的完整性,并增加连接器的机械性能。此举不仅能减少信号延迟,同时也改善了信号传输时的衰减。

| 图三 : PCI-SIG副总裁暨开发者会议主席Richard Solomon。 (摄影/篮贯铭) |

|

在今年11月举行的PCI-SIG台北开发者大会的现场,就已有数家业者展示了PCIe 5.0的解决方案,包含PCIe 5.0 CXL和CCIX的IP方案、测试与验证系统、与高速传输的重定时器(Retimer)等,为PCIe 5.0的产业应用之路,先行踏出了第一步。

「我们不希望再重蹈PCIe 3.0时代的失误。」Richard Solomon强调。

他表示,有鉴于PCIe在3.0之后开发延宕的前车之鉴,PCI-SIG正持续推动新版标准的开发进度,这也是为什么会在4.0发表之后一年,今年就宣布了5.0的规范。

频宽供不应求 PCIe 6.0将改采PMA-4

他指出,由于人工智慧、汽车电子、云端运算、资料中心、物联网与数据储存等先进应用,市场对于运算力与传输频宽的需求仍是会持续增加,因此新的规范必须不断的推进,才能够因应未来的应用需求。

依据PCI-SIG的预估,至2022年,市场的频宽需求就会达到128 GB/s,至2025年则会再倍增至256 GB/s。而身为标准制定组织,就必须要在实际需求发生之前,先行将标准底定。

「我们的期待就是领先3年左右,让制造商与相关的供应链可以有时间把产品开发完成。」Richard Solomon说。

目前PCIe 4.0的终端产品正迅速地进入市场中,PCIe 5.0的产品,也已经有了先行者,预计采用该规范的终端产品在明年就会率续亮相,至2021年就会有更多的产品导入。

然而今年最重磅的消息,还是PCIe 6.0草案0.3版本的发布,该规范才在今年十月推出。 Richard Solomon指出,新的标准将会把频宽再往上升一级,信号速率会达到64GT/s。此外,另一个大特色,是从不归零(NRZ)传输技术,演进为四阶脉冲振幅调变(PAM-4)。

| 图四 : PCB内的连结改采外接的光纤方案,以解决互连频宽不够的问题。(摄影/篮贯铭) |

|

这个变动的主要原因就是NRZ在高速传输时,讯号很容易衰减,而为了实现更高频宽的传输,因此转向PAM-4讯号。由于PAM-4能实现四种可能的电压位准,让每个符号代表2个位元,因此PAM-4技术理论上可以得到两倍于NRZ的速率。

Richard Solomon解释,使用PAM-4技术是一个新的进展,但目前仍在讨论中,而透过0.3版本的发布,也将会从会员的开发实作里取得更多的回馈,并据此再进行调整,若会员的回馈不理想,最后仍会有变动的可能性。

Richard Solomon也透露,PCIe 6.0的0.5版本很快就会推出,会更聚焦在具体的实作上,而最终的版本预计会在2021年订定。

超高速带来新的系统设计挑战

不过持续倍增的速度并不全然没有缺点,首当其冲的,就是对系统设计者带来更大的压力,不仅在整体的系统规划上需投注更大的心力,以寻求在速度与稳定度上的平衡。而在开发后段的测试与验证上,所需要的成本也将更庞大。

其中一个挑战,就是内部各元件的同步与调适。由于更高速的数据传输,意味着讯号的错误率也会倍增,如何对PCB机板上的其他元件进行调适,就成为一大挑战。也因此搭载重新计时器(Retimer)就会成为通用的设计。

再者,单一通道的频宽的倍增,也让目前的连接方案显得难以因应,尤其是在伺服器与超级电脑这类高负载的运算应用上,也因此一些PCB内部设置的连结就改采外接的光纤方案,以解决内部互连频宽不够的问题。

整体而言,PCIe 5.0和6.0的相继问世,将会对目前的元件与系统I/O设计带来全方位的影响,并有望实现次世代的高超速传输与运算效能。然而,目前既有的相关周边与PCB的设计,也需要随之进化,才有望把这个新规范的潜力完全释放。