面对开发先进元件时越发严峻的微缩瓶颈,半导体开发人员持续积极寻找创新的材料、元件结构与制程来突破物理限制。二维材料是备受全球瞩目的新兴开发选择,各界尤其看好这类材料在延续逻辑元件微缩进展方面的潜力。

| 图一 : 半导体开发人员持续积极寻找创新的材料、元件结构与制程来突破物理限制。 |

|

二维材料,例如二硫化钨(WS2),在未来逻辑晶片的制造上扮演了关键要角。它们具备杰出的材料特性,因此可望实现闸极长度的终极微缩,进而延续逻辑电晶体微缩的发展蓝图。二维材料还可能改变晶片架构的设计思维,带来革命性的巨变,甚至能让紧凑型电晶体相容于后段制程,模糊了前段与后段制程之间的分界。

近年来,实验性二维电晶体的技术成熟度已经大幅提升,而且要将这项技术引进业界的开发途径也在持续拓展。同时,为了提升元件性能,现有的相关技术挑战也在着手解决。

必用二维材料的五大理由

[1]二维材料具备多种优异的材料特性

维材料是一种能够生成二维晶体的材料。这些材料以精练的二维尺寸,展现了优异夺目的电气学、热学、化学与光学特性。其中,最著名的就是石墨烯,一种六方晶体蜂窝状的碳原子层。石墨烯拥有出色的机械强度,具备良好的导热和导电性能,还有独特的光学特性。

不过二维材料的开发其实并不仅止于石墨烯。化学式以MX2表示的过度金属硫族化物(transition metal dichalcogenide;TMD)就具备各式各样的材料特性,能够与石墨烯相辅相成。

与石墨烯不同,二硫化钨、二硫化钼(MoS2)与一些其他材料具备更广的能隙范围,所以是天然的半导体。厚度仅原子等级的二维材料,还能依照其化学组成与结构组态,分成金属或绝缘体。由于二维材料拥有优秀的材料特性,用于多元领域的契机也已浮现,包含(生物)感测、储能、光伏电子、光电电子与电晶体微缩。

[2]二维结构的电晶体可望实现闸极长度的终极微缩

在晶片制造上,像是WS2、MoS2的二维半导体逐渐崭露头角,成为在电晶体导电通道上取代「往日万用矽材」的候选材料。而它的关键优势在哪?

基于二维结构的场效电晶体(2D-FET)与矽材相比,预计更不容易受到短通道效应(short-channel effect)影响,而短通道效应已经变成矽基电晶体微缩的主要障碍。确实,随着矽基电晶体的通道尺寸越做越小,电流开始穿越这些通道,甚至在闸极电压关闭时仍出现漏电流。这被称作短通道效应,过去每进入新一代的技术节点,就会变得更严重,阻碍闸极长度进一步微缩。

鳍式场效电晶体(FinFET)是目前主流的电晶体技术,能够在某种程度上遏止这个效应。在这种电晶体结构中,鳍型的通道区域可以变得更薄,而闸极可以不只单面围绕通道。这能让闸极电压更容易控制矽基通道内的载子流动。

即将步入奈米片(nanosheet)设计的新一代电晶体结构则延续了FinFET的设计概念,进一步让闸极环绕住通道的所有面向,能够提供更有效的静电控制。不过当微缩尺寸进入3nm以下,这些矽基结构还是会持续受到短通道效应之害。

这时,具备高迁移率的WS2、MoS2就能派上用场,突破这个设计瓶颈。这些材料只要少数几层甚至是单层的原子就能构成,因此可能可以生成极薄的通道区域,电流流动的路径也会因而大幅受限,那么在元件关闭时,载流子出现渗漏的难度就会更高。如此说来,这些材料可望能实现闸极长度在10nm以下的终极微缩,消除短通道效应带来的设计疑虑。

爱美科的研究团队看好这些材料的潜力,近期进行了一项「设计—工程技术偕同最佳化(design-technology co-optimization;DTCO)」的研究,他们展示了2D-FET进一步延续逻辑元件微缩发展的可能性,其中,奈米片电晶体堆叠(stacked nanosheet transistor)的架构是最有可能的切入点。

[3]二维材料可用来建构后段制程的紧凑型开关

除了高性能电晶体,二维半导体的应用还有其他可能。其它深具潜力的应用领域包含低功耗电路,其性能和尺寸的限制都更少,例如片上(on-chip)电源管理系统、讯号缓冲器与记忆体选择器。此外,二维材料还可能可以用来突破晶片后段制程的限制,打造出能与后段制程相容的小型开关。

晶片制造可以粗略分成两个部分:制造电晶体的前段制程,以及用多层导线连接电晶体的后段制程,这步骤是要打造出具备特定功能的电路并传输电源。传统电晶体的微缩变得越来越具挑战性,科学家不断在寻找新的方法,要在后段制程放入更多的电晶体与小型电路,为前段制程节省一些空间。

不过要做到这点,只能采用可以在相对低温中进行整合的材料,这样才不会损伤下层的元件和导线。运用二维材料就有可能实现。

不仅如此,与其他的后段制程做法比较,采用二维结构的电晶体还有另一点好处,那就是它有可能可以建构出n型以及p型元件,这对CMOS逻辑元件来说有其必要。利用二维材料就能在后段制程开发紧凑型CMOS逻辑电路,用来进行电源闸控(power gating)或是作为中继器(repeater)。

[4]实验成果显示超级微缩二维电晶体的高性能

问题来了,我们能实验性地制造出这种超级微缩的2D-FET吗?它们有达到预期的性能潜力吗?近年来,科学家已经探索了多种的MX2材料。最初的结果显示,基于MoS2的材料发展较为成熟,在实验中获得的最高迁移率趋近于200cm2/Vs的理论数值。最近,基于WS2的场效电晶体也有望获得足以竞争的成果,理论上它具备更高的性能潜力。在改良接触电阻与增加元件性能方面,也皆已取得进展。

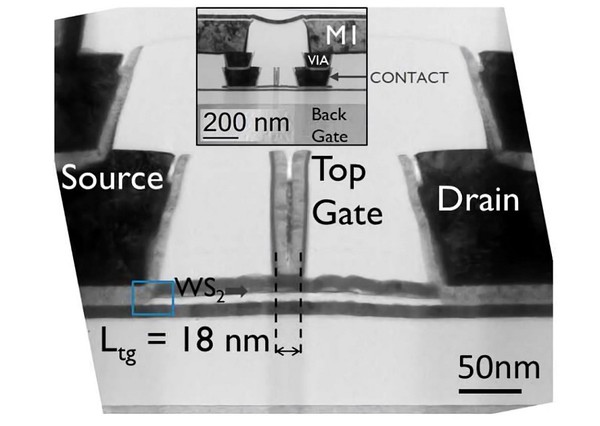

举例来说,爱美科团队能够展示具备完整功能的2D FET,而且一个通道只有1~2层单分子层的厚度,长度为30nm。我们还能用双闸极的元件结构,获得更佳的静电控制能力。传统FET只有一个闸极,位在顶层,而双闸极电晶体在顶层和底层各有一个闸极,两者连接时能增强对通道的静电控制。

[5]用于业界的2D-FET量产途径正在开发中

2D-FET要在逻辑技术节点的发展蓝图中获得一席之地,前提是要能够量产,这对产业应用来说是关键。也就是说,我们要将这些元件带出实验室,并整合到12吋晶圆上,生产工具还要符合业界标准。

爱美科已经为此做好准备,并描述了将这些二维材料导入12吋晶圆的整合流程。这套流程是用来研究不同的制程条件带来的影响,并进一步研究提升元件性能的方法。

在12吋晶圆上生成高品质的二维材料,举例而言,就能利用金属有机化学气相沉积法(MOCVD),该制程以化学反应将晶粒沉积于表面。借此,沉积的厚度能以单原子层等级的高精准度在完整的12吋晶圆上进行控制。多项实验结果显示,950℃的高温沉积对元件层的结晶度和缺陷有益。

| 图二 : 利用12寸晶圆制程打造二维元件的穿透式电子显微镜(TEM)影像。 |

|

然而,一些更复杂的电晶体架构,例如奈米片堆叠,或是在发展蓝图中属于更进阶的互补式场效电晶体(CFET),可能就需要其他的沉积技术。制造后段制程电路也是一样,这些电路的热预算有些限制。所以爱美科也调查了一些替代的沉积技术,还探索了转移制程的可行性,就是把二维的通道移至已完成部分沉积的12吋矽基板上。

开发二维材料的三大挑战

不过就现阶段,单一元件的性能比已知的那些实验性元件还低了一个数量级,而12吋晶圆的整合流程就是用来了解制程带来的影响,以及找出整合的技术障碍。

通道材料的品质以及缺陷控制还是提升元件性能的首要挑战;另一个挑战是源极与汲极接触的接触电阻,还需要降到可接受范围;最后,全方位的模型还有待开发,要嵌入在现实投产的假设情境,以实现先前所说的元件架构设计。

(本文由爱美科授权刊登;作者Iuliana Radu为爱美科计画主持人/编译:吴雅婷)