封装是属于半导体产业的后段制程,其景气循环约落后晶圆制造一至二月,且市场与半导体景气息息相关。(表一)为半导体市场产值的预估值,估计从1999年至2002年间,半导体市场将维持15﹪以上的成长。(表二)为封装市场的预估产值,在1999年至2003年间,其中DIP、CC与PGA是呈现负成长,而SO与QFP则维持缓慢的成长;但值得特别注意的是BGA与CSP的市场,其中BGA的复合成长率为16.1%,CSP为48.9%。

从这里我们可以看出整个封装型态改变的趋势,传统式的封装不再独占市场,属于先进制程的BGA与CSP已成为市场新主流。造成BGA与CSP迅速成长的原因为何?我们近年来IC产品的走向朝着以下的趋势发展:1.轻、薄、短、小;2.高I/O数;3.良好的电性与散热要求。所以我们不难了解BGA与CSP的快速成长乃是其符合市场的需求。

另外,Flip Chip开发至今虽已有30年以上,但由于其专利期限已过,故目前为封装厂相继研发的重点,而成为高阶封装的主流之一。本文将以高阶封装市场为主题来探讨PBGA、CSP与Flip Chip的现况与发展。

高阶封装市场概况

PBGA市场概况

PBGA封装为目前高脚数封装之主流,已广泛地应用在芯片组IC(Chipset)、LCD Panel控制IC、绘图芯片与高阶交换器IC。传统的导线架封装,受到间距(Pitch)的极限限制,其出脚数被限制于256脚以下,故脚数超过300脚以上之IC多以PBGA为最佳选择,同时PBGA也被证实较QFP有更佳之电性与散热特性,对于高速运转之IC所产生的高热有很好的散热效果。

目前市场上的规格已标准化,常见的规格有27x27、35x35、37.5x37.5与40x40。其中27x27应用于LCDPanel控制IC及网络交换器IC,35x35与37.5x37.5锁定于芯片组市场,而40x40则用于高阶处理器(如Layer-3网络交换器芯片)。

由于SOC(系统单芯片)及多芯片模块(MCM)的概念兴起,IC的功能越来越多,也越复杂;并随而来的就是更多的I/O数与更严格的散热要求,这都是PBGA市场逐渐成长的原因(表三)。

CSP市场概况

近年来拜快速成长的移动电话、可携型个人数字助理(PDA)与笔记本电脑之赐,促成了CSP(Chip-Scale Package)封装市场的快速掘起。所谓CSP一般的定义为:1.封装产品的长度及宽度

此外,藉由芯片的堆栈技术,在一颗成品内整合3种芯片绝非难事,如此大幅节省厂商生产成本与IC所占空间,如Flash Combo便是一例。目前全世界发展CSP的封装方式超过40种以上,无法以单一的封装方式作为整个的代表。

(表四)将CSP分为四大类型,其中BGA CSP(Fine-Pitch BGA,或Mini BGA)之材料成本逐渐下降,而使其成为CSP市场上的主流。同样归为CSP的μBGA一直存在着两个重要的问题,其一是居高不下的成本,其二是Socket规格不统一的问题。

随着芯片大小的不同而会造成封装成品大小的不同,这会造成Socket选择的复杂性或增加厂商的模制具投资成本;故缺乏标准化的封装成品为其主要的缺点。此外IC设计者应有很高的自由度来改变芯片的大小(例如改以0.18微米设计取代原先之0.25微米),以降低成本,但却不能因成品的大小一再改变而增加其顾客在PCB设计(Layout)上的困扰。

至于来势冲冲的Flip Chip在CSP市场中也遭遇到居高不下的成本与缺乏标准的Socket问题,使得其市场一直裹足不前;所以Flip Chip便将其主战场移至更高脚数或对于散热有高度要求的产品中。

CSP的应用方面以追求轻薄短小的产品居多,尤以移动电话及可携式电子产品之内存为最。在内存方面广泛地应用在Flash、Low PowerSRAM、Flash Combo、DRAM及RambusDRAM。而未来高频的DDR DRAM推出,因其更强调封装的电器特性,故可望采用BGA的封装方式,BGA CSP最有可能因成本优势成为最佳选择。

Flip Chip市场概况

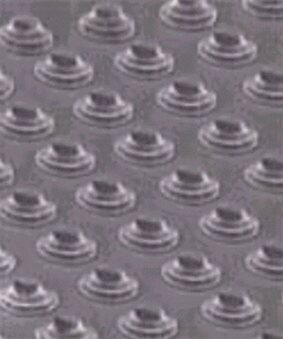

Flip Chip的封装方式不同于目前的打线方式,是以锡铅凸块(Solder Bumps)或金凸块(Gold Studs)直接生长在晶圆表面之后,再将芯片正面朝下直接使芯片上的pad与基板(substrate)结合的技术。如此一来缩短了芯片与基板间的距离,加快了讯号传输的速率。由于芯片背面不需加Molding,除了使组件更轻外,也提高了散热效果(图一)。

| 《图一 Bumping at Flip Chip》 |

|

另一与打线技术不同之处,在于基板与芯片间的填充(Underfilling)制程。它除了具备足够的接合性与防止可能的污染物之外,更要能抵抗在做接合时因热膨胀(CTE;Coefficient of Thermal Expansion)所发生的不一致缩胀(Mismatch)与减低凸块所产生的应力,此点对厂商来说是很难克服的一道障碍。

当芯片的I/O数增加的同时,以四周出点方式有时已无法符合设计上的需求,故设计者会将I/O分布至全区域或部份区域,这时就不能利用打线方式来进行封装,Flip Chip是唯一选择。此外,Flip Chip被大量采用在计算机用的高阶CPU封装,因该产品对于散热有严格的要求。

高阶封装市场的未来发展

由于PBGA、CSP与Flip Chip目前技术多已成熟且广泛地应用在各类产品上,但基于产品的特性与需求各异,而使不同技术在不同产品市场中的发展也有所差异,故以下将市场分为低脚数与高脚数市场,更可清楚的看出此三种封装的市场定位及发展(表五)。

低脚数市场

相同的芯片使用TSOP或SO封装,其成品面积约为使用CSP封装之6至8倍,在面对轻薄短小的趋势下,TSOP与SO已无法满足小体积的要求。就移动电话的内存来说,即使是多1mm的差异就不能被放入成品基板之中了,故CSP取代了TSOP与SO在低脚数市场的地位。

但是CSP的种类甚多,要采用BGA CSP、μBGA抑或Flip Chip?就前面所提,μBGA虽然能将产品封到接近芯片大小,然而BGA CSP也很容易做到,且少了很多μBGA存在的问题,这也是μBGA一直未起来的原因。Flip Chip由于其产业结构(Infrastructure)并未成熟,故其成本无法有效地降低,除此之外,它还有其他技术上的问题。

表面黏着设备兼容性

在封装成品与PCB的黏合制程中,BGA可使用相同的SMT设备而不需要变更其它制程,但Flip Chip在经过SMT之后还要加上另一样填充(Underfilling)的制程,这样一来提高Flip Chip在SMT制程中的不稳定性与复杂性。

重工性

在SMT过程中,无可避免的会发生重工的情形,故产品被要求有很高的重工性(Reworkablility),以BGA 而言,使用标准的SMT设备即可以进行重工,但Flip Chip一旦经过填充制程后,就不太可能重工了。

可测试性(Testability)

通常Flip Chip (此指COB;Chip on Board)一旦上了SMT之后就无法进行测试,在无法得知芯片的电性之下,大大地提高了厂商的风险。BGA在封装完成后即可交由测试厂进行测试。

由上可知BGA CSP占尽了优势,而市场上的趋势也显示着BGA CSP正迅速地成长并成为CSP的霸主。

高脚数市场

目前在超过100脚至256脚间的产品多数仍采用QFP,但以低成本为号召的QFP正因BGA的成本逐渐下降而受到严重的挑战。在数年前每只脚平均价格BGA约为QFP之两倍,如今在100脚至208脚的封装中,BGA的价格几乎与QFP一致。BGA已有逐渐取代QFP之趋向。在超过256至600脚间仍以BGA为主流。另在特殊应用市场,如更高脚数(1000脚以上)或高散热需求产品,还是以Flip Chip为最佳选择。

由以上的分析中可看出,未来几年内,在低脚数市场BGA CSP将仍维持其主流地位;而在高脚数的封装市场中,则是BGA与Flip Chip的互争高下,如有兴趣,欢迎至www.neopac.com.tw查询。(本文作者目前任职于讯捷半导体)