目前 PFC 階段和 DC/DC 階段對電源供應的效率需求越來越高,尤其是在輕負載運作下。為滿足這些需求,工程師合乎邏輯的選擇就是使用閘極電荷較低的 MOSFET,以減少驅動損耗。在整個負載範圍內,低閘極電荷能讓開通及關斷實現快速的開關切換。但是,這種選擇也存在部分缺點。由於閘極振盪的關係,因此工程師必須選用較高的 RG,ext 降低開關速度,或是使用鐵氧磁珠來抑制這些振盪。

但是這兩種方式都要花費很長的工程設計時間,還會增加設計成本。因此工程師必須找出既有很高的效率,又不用花太多時間重新設計,就能輕鬆融入系統設計的功率 MOSFET。第二項特點通常稱為「易用性」。工程師不只要解決這些挑戰,還必須試著降低物料清單成本。其中一個方式,就是在 PFC 和 DC/DC 階段選擇相同的 MOSFET;除了高效率及「易用性」這兩項需求之外,DC/DC 階段的硬式整流還需要有耐用的本體二極體。

CoolMOS P6 是 600V CoolMOS 系列最新的裝置,專為滿足所有這些應用需求所設計,一次全部解決高效率、「易用性」程度,以及 PFC 階段和 DC/DC 階段的多重用途等問題,可節省設計的時間及成本。

1.1 @大標:目標應用

新的 CoolMOS P6 係針對典型的 AC/DC SMPS 功率架構的各種應用而設計。

P6 技術適用於硬式切換的 PFC 階段,及軟式切換的 DC/DC 轉換階段。600V P6 包含下列的目標應用:

以下的技術參數為判斷 P6 技術在此類應用中之效率的關鍵因素。

1. @中標:降低閘極電荷 (Qg)

CoolMOS P6 最重要的改善之一就是降低裝置的閘極電荷,減少閘極電荷 Qg可帶來多項好處,尤其是在低負載條件下的驅動耗損。相較於 CoolMOS E6,P6 可減少 30% 的 Qg,其主要來自於平台狀態電荷的減少,還可實現快速的開關切換。

2. @中標:整合式閘極電阻 (RG)

為了平衡快速的開關切換以達到最高效率,同時為了不要犧牲「易用性」和良好的操控性,CoolMOS P6 整合了較小的整合式閘極電阻 RG。這個體積小巧的整合式 RG 可在正常工作電流條件下實現快速的開通和關斷,在異常條件下也能限制 di/dt 及 dv/dt。

3. @中標:高閘極閾值電壓 (Vth)

在 LLC 和 ZVS 這類的諧振拓樸中,雖然能夠消除開通耗損,但關斷耗損仍然在總耗損中佔了很大的比例。高閘極閾值電壓 (Vth) 可以提前關閉 MOSFET,進而提高效率。

英飛凌先前的 CP 和 E6 技術都將 Vth 的典型?定為 3V。根據此一特性我們可發現,採用 P6 技術會將 Vth 提高到 4V 的典型?。從切換速度可看出,P6 的開關斜率明顯高於 E6,而且很接近 CP,不只減少開關耗損,更提高功率轉換的效率。

4. @中標:dv/dt 額定?增加至 100V/ns

SJ-MOSFET 的 MOSFET dv/dt 典型額定?為 50V/ns。工程師受到此資料表參數的限制,只能透過低 RG,ext 強制進行快速切換,實現高效率的應用。由於 P6 的 Qg 較低,且電容量較少,加上有 12 年的製造經驗,P6 技術已能將 dv/dt 從 50V/ns 額定?提高到 100V/ns。

圖 1 顯示 E6、P6 和 CP 在最大電阻 RDS(on) 190 m? 範圍內 dv/dt 測量值的比較。CP 的 dv/dt 最大值為 50V/ns,斜率較高。相較於 CP,P6 技術的 dv/dt 更為平穩,且控制程度也獲得提升。即使在最小的 RG, ext 下,P6 的 dv/dt 仍低於 50V/ns。

P6 技術是一項非常穩定耐用的技術,可承受超過 50V/ns,而不會發生特性上的變化。改善 dv/dt 之後,可以減少外部 RG,進而提高效率。

「易用性」,P6 閘極振盪

圖 2 顯示 IPP60R190P6 在 PFC 中的典型開關切換波形。該測試電路配置了一個額外的 7.2pF 外部閘極電容,模擬閘極和漏極與 PCB 之間耦合的寄生電容。設計人員在佈線時應特別注意,盡量減少此類的寄生電容,才能確保 MOSFET 的最高效能。在此一測量中,190m? 裝置採用 5? 的外部 RG。

切換波形採用 VDS=400V (顯示為綠色) 和 VGS=13V (顯示為深紅色) 進行測量。顯示為黃色的電流波形在每次脈衝時都會增加,直到飽和為止,其表現為峰值電流為 75A 時 VDS 的偏移。P6 具備最佳化的 RG,可呈現出良好的切換波形,而不會影響 VGS 規格限制。

@中導通本體二極體的硬式整流

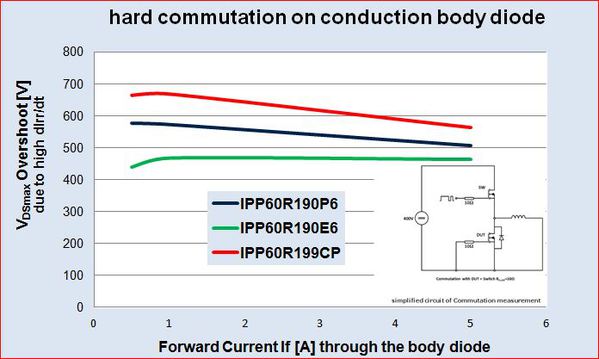

軟切換應用需要對導通本體二極體進行硬式整流,而且需要在本體二極體的高整流耐用性和快速切換特性之間求取平衡。快速切換裝置所有的屬性 (高 di/dt、低 Qg、低 RG) 可使導通本體二極體在硬整流期間產生較高的電壓峰值。圖 3 顯示在 10μs 本體二極體導通時間過後硬整流的電壓峰值 (正常操作條件下,本體二極體的導通時間不會超過 400ns)。

| 圖三 : 600V P6、E6 和 CP 之間的導通本體二極體硬式整流比較 |

|

圖 3 顯示整流中 dIrr/dt 較高而導致 VDSmax 過衝。測試裝置與開關裝置的 RG,ext 相同為 10?。VDSmax 過衝將受到佈線的寄生分量、外部 RG 和開關的切換速度影響。相較於 CP,P6 的整流行為較佳。

測量結果

本小節顯示實際應用中的測量結果,展示 CoolMOS P6 在硬切換和軟切換應用中的優點。

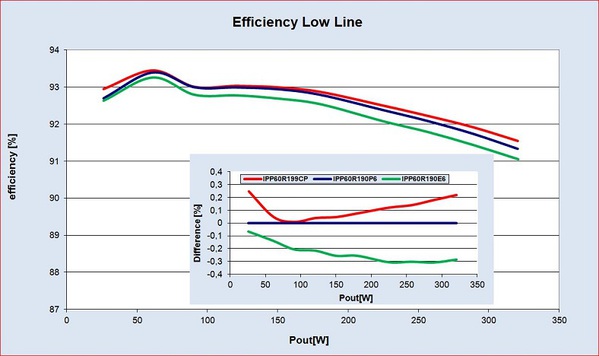

CCM PFC 中 300W PC Silverbox 的效率測量

此測量在 190m? RDS(on) 範圍內將 600V P6、E6 和 CP 進行比較。

設定參數:

‧ Vin=90VAC

‧ Vout=400VDC

‧ Pout=0W 至 300W

‧ 頻率=65kHz

‧ RG,ext=10?,採隨插即用方式,對 600V P6、E6 和 CP 等裝置進行比較

| 圖四 : 600V P6、E6 和 CP 在絕對效率 (上) 和相對效率 (下) 的比較 |

|

這種隨插即用的測量方式,顯示 CoolMOS P6 相較於 CoolMOS E6 和 CoolMOS CP 的優點。在 300W 連續導通模式 (CCM) 下的 PC Silverbox,輸出功率達到 70W 以上時以 CCM 運作,否則以 DCM 運作。即使在輕負載條件非同等對比的情況下,P6 的效率仍有小幅上升。當輸出功率超過 70W 時,以 CCM 運作,相較於 E6,在滿負載條件下 P6 的效率可提高 0.2% 至 0.3%。由於 Qg 降低和相對較高的 Vth,因此效率得以提高。

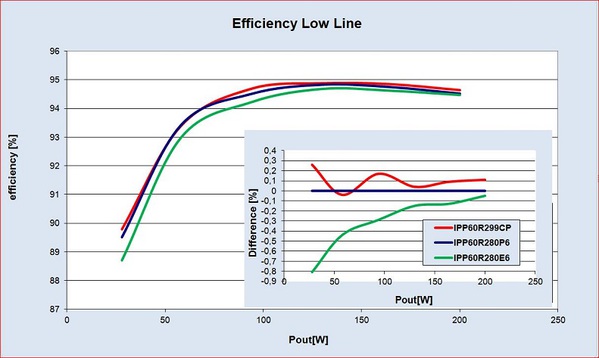

1.2 @大標:LLC 階段中 200W PC Silverbox 的效率測量

@內文此測量在 280m? RDS(on) 範圍內將 600V P6、E6 和 CP 進行比較。

設定參數:

‧ @內標:PC Silverbox LLC 階段 200W

‧ Vin=90VAC

‧ Vout=400VDC

‧ Pout=0W 至 200W

‧ 頻率=65kHz

‧ RG,ext,開通=27?

‧ RG,ext,關斷=10?

‧ 採隨插即用的方式對 600V P6、E6 和 CP 進行比較

| 圖五 : 600V P6、E6 和 CP 在絕對效率 (上) 和相對效率 (下) 的比較 |

|

在這個 LLC 測量中,相較於 E6,P6 在輕負載條件下的效率提升超過 0.8%。效率的提升同樣是因為 Qg 相較於 E6 減少 30%。在滿負載條件下,P6 和 E6 測得的效率結果相近,因為其 RDS(on) 等級相同,這在滿負載條件下為重要參數。

使用 600V P6 的設計指南

關於如何使用 CoolMOS P6 以最佳的方式實現效能,以下小節提供部分相關指引。

1.3 大標:最小外部閘極電阻 (Rg,ext)

在設計良好的電源供應中,我們建議使用極低的外部電阻,開通時最小電阻為 5 歐姆,關段時電阻為 0 歐姆。由於採用 Rg,int 和非常穩定耐用的 CoolMOS P6 設計,因此可以使用這種高效的 Rg。不過,選擇外部 Rg 始終取決於 PCB 寄生元件,這是因為來自 L stray *di/dt 的電壓訊號和來自 C parasitics *du/dt 的電流訊號,這些寄生元件會在 MOSFET 上產生超乎預期的峰值電壓或峰值電流。為避免此類峰值,建議減少寄生元件或提高 MOSFET 的 Rg,ext。

1.4 @大標:600V P6 的並聯

要並聯 600V P6 時,一般建議在閘極上使用鐵氧磁珠或分離的圖騰柱。

結論

在目前的 MOSFET 市場上,大多數裝置的易用性及可用效率各不相同。有些裝置提供最簡單的操控性,因此也具有最高的易用性,在效率方面僅有些許減損。有些裝置則提供最高的效率,但由於切換速度較快,因此在設計時需要特別注意。CoolMOS P6 的推出解決了這類的問題:這些裝置除了滿足高效率的需求,同時也不犧牲易用性。透過良好的平衡技術,就能得到最佳易用性和效能的裝置。