此篇访谈中,比利时微电子研究中心(imec)先进图形化制程与材料研究计画的高级研发SVP Steven Scheer以近期及长期发展的观点,聚焦图形化技术所面临的研发挑战与创新。

本篇访谈内容,主要讲述这些技术成果的背後动力,包含高数值孔径(high NA)极紫外光(EUV)微影技术的进展、新兴记忆体与逻辑元件的概念兴起,以及减少晶片制造对环境影响的需求。

怎麽看待微影图形化这块领域在未来2年的发展?

Steven Scheer表示:「2019年,极紫外光(EUV)微影技术在先进逻辑晶圆厂进入量产,如今动态随机存取记忆体(DRAM)厂商也对采用EUV制程越来越感兴趣。这一切都要归功於艾司摩尔(ASML)的倾心倾力与坚持研发,有了他们的助力,这项技术才能取得超??意料的重大突破。新一波革命是引进高数值孔径(0.55NA)的EUV微影技术,把光学成像的半间距(half pitch)缩小至8nm。

新一波革命是引进高数值孔径(0.55NA)的EUV微影技术,把光学成像的半间距缩小至8nm。

为了推动业界采用高数值孔径的EUV微影技术,imec与艾司摩尔正在联手创建高数值孔径极紫外光实验室(High NA EUV Lab),用来满足High-NA晶片制造商在早期开发阶段的需求。同时,我们也在更广泛的生态系与图形化设备与材料厂商合作,藉此开放High NA实验室的资源,并筹备EUV光阻剂材料、涂料底层、乾式蚀刻、光罩、解析度增益技术(resoulution enhancement technique)与量测技术。」

引进High NA技术有何优先考量?

「High NA工具的可用性显然是首要之务。在模组与光学元件的整合技术方面,艾司摩尔与蔡司目前取得亮眼进展。虽说在制程方面,为了引进低数值孔径(low NA)的EUV技术,创新的解决方案至今仍在持续开发,但未来还需更多的技术革命,才能有效导入High NA EUV技术。除了High NA工具,EUV光阻剂一直是imec与生态系夥伴的研发重心之一。High NA EUV微影技术的进展将能在较短的焦点深度(depth of focus)下,进一步提升光学解析度并缩小元件的特徵尺寸。这自然会导致光阻薄膜的厚度下降,因此需要利用新兴光阻剂与涂料,以优化蚀刻阶段的EUV吸收与图形转移。

此外,我们还要持续推动改良随机性粗糙度的问题,甚至是我们几年前发现采用EUV进行图形化所面临的光阻剂缺陷问题。就光阻剂的图形化性能来说,过去都以解析度(resolution)、线边缘粗糙度(LER)或局部线宽均匀度(LCDU)以及敏感度(sensitivity)为性能指标,三者合称为RLS叁数。

但现在考量到随机性的重要,因此在早期研发阶段新增了第四个图形化性能指标,也就是缺陷(failure),藉此反映制程受随机性影响的操作范围限制。针对由光阻系统诱发的随机缺陷,我们相信势必会有解决方案能减缓这些问题,同时放宽制程的操作范围,并降低光阻剂量,我们也计画携手夥伴在High NA实验室一同展示这些新技术。

降低特徵尺寸与光阻薄膜厚度也会影响量测技术。除了转印性能,大幅降低光学成像尺寸有可能会拉低准度(accuracy)与精度(precision),进而带给量测与检测性能负面影响。

如何协助应对EUV光阻剂的挑战?

「针对传统多成分混合光阻系统的化学随机性问题,也就是除了散射杂讯以外的随机现象,我们正在研发新兴材料。例如,含金属光阻剂或单成分光阻剂。imec持续协助材料供应商进行概念开发及像是污染风险和制程整合技术等关键问题评估。

新型High NA EUV光阻系统的研发工作不能各自为政,为了达到最隹成效,就必须在涂料工程、新型硬罩与高选择性蚀刻制程方面进行协同优化。面对这项挑战,imec近期开发了用来配对光阻剂与涂料特性的全新工具箱。经过材料筛选、表面能匹配研究、材料物理特性分析与介面工程,采用旋转涂布或沉积制程的涂料底层(underlayer)薄膜就能与光阻剂一起曝光,形成更微距的EUV图形,并优化在LER、敏感度与缺陷度(defectivity)方面的表现。

除此之外,为了加速材料开发,我们建立了图形化材料特性分析的基础结构,称之为Attolab的工具箱,用以解析光阻剂与涂料底层在EUV曝光时的行为表现。现在研究薄膜与堆叠的吸收系数与层解析(layer-resolved)结构特性时,就能搭配辐射测量及反射测量,这些技术都开放给Attolab研究夥伴使用。

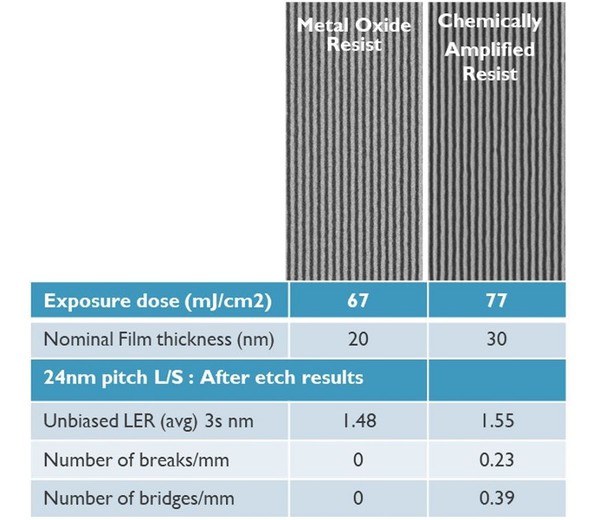

| 图一 : 24奈米线宽(line)与间距(space):金属氧化物阻剂(metal-oxid resist;MOR)与化学放大型阻剂(chemically amplified resist;CAR)的图形化技术开发。MOR所需的剂量较低,且在厚度较薄的情况下,LER与缺陷表现仍较隹。 |

|

为了推动新一代微影技术,imec还探索了哪些发展方向?

「现阶段正在开发几项新型光罩技术。为了减少EUV曝光剂的用量,目前锁定具备低折射率吸收层的光罩技术展开积极研究,因为这些光罩能在使用低曝光剂量的情况下,产生对比度或正规化影像对数斜率(normalized image log slope)较高的空间强度轮廓。

imec也考量到晶圆图形化的随机性误差与光罩的3D成像效果,也就是光罩3D拓扑空间影像的失真问题。晶圆上的随机缺陷成因很多,光罩的变异性(variability)就是其一。为了解决这项问题,我们研究有哪些类型的光罩变异性(包含不同粗糙度)较易导致晶圆上的随机缺陷,以提出光罩及空白光罩的新版规格为目标。

此外,High NA EUV曝光机将会采用变形镜片,这使得x轴与y轴的放大倍率并不一致。该变形现象代表着晶圆势必需要进行图形接合,以此取得与其它传统光刻技术相同的曝光区域面积。晶圆图形接合较着重在光罩曝光区域边缘的品质,以及可能用来减缓边缘缺陷的方案。

深入了解光罩与EUV光学的交互作用越来越重要,有监於此,imec整合了完整的光罩研发生态系统。透过与光罩及空白光罩厂商合作,我们协助光罩创新(像是新兴吸收剂)产业化,以及探索光罩的复杂特性(像是变异性或图形接合),这些都在imec与艾司摩尔共同建立的High NA EUV实验室执行并经过模拟。

这些问题都不是引进High NA EUV技术的主要障碍。但为了以无阻、快速且高成本效益的方式引进最高效的High NA EUV技术,积极应对这些挑战,并提供生态系统内的关键厂商一套有效的合作平台,至关重要。imec与艾司摩尔当初以世界首台High NA曝光机为中心而创立High NA EUV实验室,主要目标就是推动业界尽速导入High NA EUV微影技术并扩大其产能。」

图形化领域在未来2~5年会受到什麽其它发展影响?

「除了EUV微影技术的创新,逻辑及记忆体的新兴元件概念越来越常采用三维的结构设计,这也会带给特殊图形化技术一些新的契机。

互补式场效电晶体(CFET)是继闸极环绕(GAA)奈米片之後的新一代元件架构,其运用了在FET通道上堆叠另一个FET元件的概念。制造CFET元件需要具备高深宽比的图形化步骤,才能制出主动元件、闸极、源极/汲极凹槽蚀刻,以及中段制程的M0A层接点。另外,大量的材料蚀刻也将必不可少,像是金属或介电材料等。

在减少CFET制程复杂度方面,由下而上的沉积设计或区域选择性沉积(area selective deposition)等创新方法能发挥重要作用。接着,CFET元件可能会与晶背供电网路(BSPDN)整合,使得CFET标准元件从5轨微缩至4轨设计。这种新型布线方法需要高深宽比通孔的蚀刻技术及自对准的图形化技术,且对闸极侧壁呈现良好的蚀刻选择性。

逻辑及记忆体的新兴元件概念越来越常采用三维的结构设计,这也带给特殊图形化技术新的契机。

在记忆体方面,动态随机存取记忆体(DRAM)目前是以扁深构形的电容作为记忆体单元。为了增加记忆体密度而微缩间距时,电容的横向关键尺寸(CD)会持续缩小,且其构形必须越来越高,才能维持相同的电容。这不仅会带来制造问题和产量损失,我们更预期2D DRAM将会触碰材料的基本底线。

为了克服这些问题,不同的3D DRAM制程现已纳入考量,模组相关的主要挑战也在设法解决。可以想见半导体氧化物等新型材料将会获得采用,另以高深宽比蚀刻及横向凹槽蚀刻等数道步骤作为辅助,但这些在许多方面仍面临了挑战。其次,就技术难度而言,以衬垫层、介电材料及金属填补纵向孔洞及横向凹槽预计会至少与3D NAND快闪记忆体技术相当,极具挑战。」

| 图二 : imec先进图形化制程与材料研究计画的高级研发??主任Steven Scheer。(source:imec) |

|

imec团队在研究制程与材料时,如何协助推动永续制造?

「就现况预估,晶片制造约占了0.1%的全球碳排放。虽然如此,由於先进制程越来越复杂,制造逻辑晶片所衍生的二氧化碳排放估计会在未来10年翻倍。同时,晶圆的总产量预计也会每年增加约8%。若不采取行动,晶片制造产生的碳排量将在未来10年成长4倍。根据巴黎协定,所有产业都该在每10年减少一半的碳排放。换言之,要是我们「放手不搏」,晶片产业距离减排目标将会相差8倍。

因此,imec研究的其中一项重点就是永续性。我们已经发起永续半导体技术与系统(Sustainable Semiconductor Technologies and Systems)研究计画,集结晶片制造供应链,以净零碳排为共同目标。为了量化一般晶圆厂所带来的环境影响,我们也在建立名叫imec.netzero模拟平台的虚拟晶圆厂。藉由与设备与材料厂商建立合作,目前已开发的模组仍在研究测量基准与进行验证。

在2023年国际光电工程学会(SPIE)先进微影成形技术会议(Advanced Lithography and Patterning Conference)上,imec展示了先进晶片图形化制程对碳排放影响的量化评估方案。在imec的实体晶圆厂,高影响力领域也已确认并锁定为解决方案的目标。例如,减少含氟的蚀刻气体用量、减少用水量、回收稀有材料、回收氢气及降低微影制程的化学剂量。

在开发新一代技术的同时,还要面对其带来的环境影响,似??是令人却步的艰难任务。的确没错,但我们做得到。晶片产业以创意及创新闻名,而我们现在只需加上一条开发要件:减少环境影响。」

(Steven Scheer为imec先进图形化制程与材料研究计画的高级研发??主任;编译/吴雅婷)

*刊头图(source:imec)