为了实现像是由人工智慧(AI)驱动、具备情境感知与半自动能力的数位双生等未来科技应用,现代的运算系统需要超越摩尔定律,在性能方面达到数倍升级。

要让每总体拥有成本(TCO)的晶片性能跃升,系统级设计、软硬体(电晶体)协同设计优化、同时探索先进算力,以及多元化的专业团队与能力,全都至关重要。

在数分钟内完成血液滴样的基因体分析或蛋白标记,同时降低检测费用。提供高动态无损的扩增实境(AR)与虚拟实境(VR)环境,实现流畅互动。信赖半自动化且具备情境感知能力的AI私人助理,对我们个人的数位双生进行监控。展??未来,透过整合高效能运算与AI系统,人类似??获得了改善生活的无数可能。然而,这些可能至少会受限於现有的运算系统,包含其运算能力与节节升高的成本。这项挑战不容轻视,因为这些新兴应用全都需要晶片性能与能源效率达到数倍升级,同时抑制成本增加。

很可惜,运用目前的高效能或AI硬体,我们很难以传统的微缩技术来建构这样功能强大的系统。我们不能为了达到目标而一味增加处理核心或记忆体,这会导致元件尺寸、能耗与成本呈现不合理地爆炸性增长。

那我们为何不一如既往,延续晶片微缩规模呢? 有哪些主要困难? 此外,我们能采取什麽策略来提升运算能力与能源效率,同时顾及整体成本?

系统微缩的门槛调高

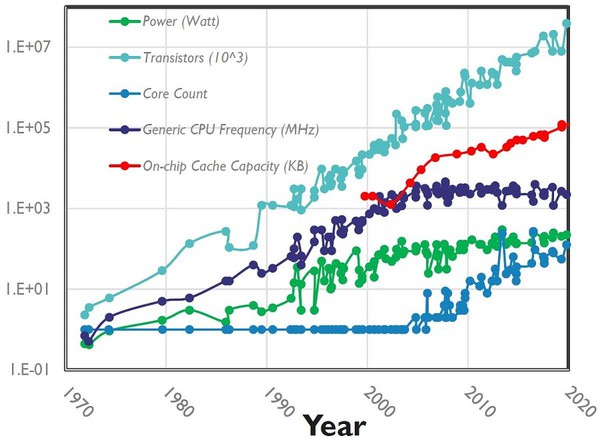

50多年来,摩尔定律与Dennard缩放定律一直是晶片性能代代升级与维持稳定成本的基础;前者意味着在相同的晶片面积与成本下,电晶体数量大约每两年翻涨一倍,後者则是在电晶体微缩时维持功率密度不变。但在过去10几年间,受到这些定律启发的尺寸微缩策略显然不再能满足未来运算系统的微缩目标。其中包含好几项因素,我们称作微缩障壁(scaling walls),可分为尺寸障壁、记忆体/频宽障壁、功耗/热障壁以及成本障壁。

虽然相同面积下的电晶体数量还是维持每两年翻一倍,但业界在采用复杂的系统设计时面临了超??常理的高昂成本,以及处理速度与功耗问题。举例来说,在传统的冯纽曼电脑架构下,晶载快取记忆体的微缩速度已经赶不上逻辑元件,而且传输速度也越来越难达到处理器所需的水准。除了记忆体/频宽障壁,漏电现象也破坏了Dennard缩放定律的发展,导致散热与频率停滞问题,与此同时,先进制程的成本也在??涨。

从架构着手,在系统单晶片导入复杂的记忆体阶层、多核处理器与专用加速器(xPU)成为克服这些微缩障壁的解决办法。尽管目前多核设计当道,处理器随着微缩技术演进而步入先进制程,但在改良性能、功耗、尺寸与成本(PPAC)方面却开始面临发展饱和。

| 图一 : 采用传统冯纽曼架构的处理器性能演变,包含电晶体数量、核心数量、功耗、CPU时脉、快取记忆体速度。 |

|

万物齐涨 着手解决「创新者困境」

加上随之而来的庞大成本障壁,可见「算更快、省更多」的快乐微缩时代已经结束。过去,半导体产业在考量成本时较为狭隘。据分析,每采用新一代制程技术,每平方毫米(mm2)的相对成本都会减少,如同摩尔定律的预测。然而,半导体制程与系统设计日趋复杂,因此整体成本不再下降。除了先进制程的封装成本上扬,系统运作期间的散热与功耗、设备维护等,都在逐步拉抬总体拥有成本。因此,每总体拥有成本的性能正在下滑,相同尺寸下的系统成本也在逐渐增加。

这些因素造成了所谓的「创新者困境(the Innovator's Dilemma)」,这也是所有企业在运营既有业务的同时,投入破坏性创新开发与投资时都会面临的挑战,这些业务透过导入能维持市场价值的永续科技,进而将其推向市场。考量每总体拥有成本的性能升级幅度,当前的挑战是持续推动技术快速升级,比照我们见证的AI与高效能运算发展。实现数倍的性能升级是我们研发的主要动力。

我们确信,要取得运算效能的空前进展,唯一方法就是动用整体晶片系统的创新资源,涵盖演算法到核心元件。而且这些创新应该从最一开始就进行协同设计才能确保整体成本最隹化。这些原则是比利时微电子研究中心(imec)运算系统架构(Compute System Architecture)研究项目的指引。

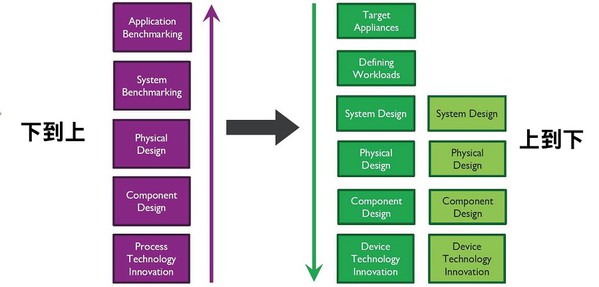

颠覆传统 由上而下的系统设计

系统设计的思维是由上而下建立整体系统架构。传统上,摩尔定律的微缩进程驱动了不少技术发展:有了全新的电晶体架构就能开发新兴元件,接着就能堆叠元件,设计更高效的电路、记忆体和处理器。然而,这种由下而上的设计方法限制了整体晶片系统进行协同设计的可能性。

| 图二 : 比较「由下而上」的传统方法与「由上而下」的设计方法。 |

|

以系统架构为考量的设计方法认为应用需求势必会驱动解决方案。我们要让目标装置驱动元件与系统架构的创新,而不是选用现有硬体来解决问题。我们正在发展一种设计思维、框架与研究方法,使得整个元件都能持续进行由应用驱动装置的协同设计。

具备时下影响力的应用将会推动系统开发,预测未来几年的产业与社会需求。

从架构到技术的优化循环

开发未来的运算系统架构,先要了解目标应用的需求,以及背後运作所需的关键规格与演算法。

假设我们以全基因体快筛为目标应用,那麽适用的规格可能是要用来分类基因缺陷。随後,我们针对目标应用来预测未来需要采用的软体、运算系统与关键元件模组,把整体系统纳入考量:我们界定不同抽象层所需的创新,包含演算法、架构模型化、性能分析与实际执行。

接着,架构模型化与分析提供每总体拥有成本的预期系统性能,并提出设计建议以实现目标性能。在系统层级取得的性能优势将会源於不同抽象层之间的各种交互优化。这些优化相辅相成,理想的话还能带来数倍的性能升级。这就是根本性重复的协同设计循环。

这套模型以总体拥有成本的性能为指标,该指标带领我们进入後续流程。这套流程可能包含重构演算法、评估不同的系统设计,甚至可能进行原型设计,藉此开发具备规模化、可靠度与能源效率的架构概念验证,提供新一代应用所需的高效能运算。

研发要件:从建模、後摩尔运算到多元多样的研究团队

现有的模型功能不够强大,无法从新型系统定义中模拟与撷取有关元件性能的资讯。因此,我们开发了全新的微缩化建模与模拟技术,目标是超越现行模型的精度与速度。

这些模型本身包含了不同技术模组的特性,这些新型技术量能将能抑制系统微缩的挑战,涵盖封装到运算单元到软体创新。为了验证这些模型的成果,我们希??能在系统开发的各个阶段建立关键技术模组的原型。技术不只有硬体元件,还有演算法、中介软体、程式设计模型与网路堆叠,一路延伸到软体开发,以及用户与装置的互动。

就基本技术而言,考量现有的矽材技术,例如先进光学I/O与3D制程技术,并探索新兴AI演算法与後摩尔时代的替代运算方案。这就囊括量子运算、光学计算设计与超导数位运算,可??在功率效率、运算密度与导线频宽方面取得超前进展。

模拟与技术方面的挑战难以解决。但是毫无疑问,研究团队是最大资产,促使此次研究获取成果。这批跨域多元的研究人员具备演算法研究、软体开发、异质整合系统编译器与中介软体、微架构以及电路设计等不同背景。他们都渴??且具备能力跳脱框架,希??能带来富有意义与影响力的全新想法。

(本文为imec提供;作者Arindam Mallik、Boris Leekens、Eric Mejdrich;编译为吴雅婷)