XMOS Semiconductor宣佈其矽晶及beta設計工具業經測試,測試晶片並已由台積電透過90奈米G製程生產。XMOS針對可配置半導體元件所提供的創新多處理器方法,為廣泛的消費性應用提供了全新層次的彈性與低成本優勢。

|

| XMOS Semiconductor發表第一款SDS |

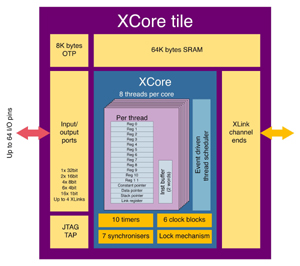

MOS技術核心為一稱為XCore之精簡、事件驅動(event-driven)、多執行緒處理器。透過以達8個執行緒分享500MIPs運算能力,XCore引擎可輕易地導入一系列複雜的硬體功能。其運算及控制功能可透過廣為熟知的嵌入式軟體設計流程存取,設計者並可運用C語言迅速地將white-board功能規格繪入矽晶中。

XMOS技術長暨創辦人David May表示:「我們估計全球大學正為每位硬體工程師提供20至30位軟體設計者,這並不令人意外,因產品差異化的責任大量地依賴於軟體領域。透過發表此可存取及廣為熟知的處理器架構,並緊密耦合事件驅動系統及多執行緒原理,我們正提供今日矽晶設計者其真正所需之工具。」

XCore處理器透過一事件驅動之輸出/入埠緊密地與外界連結,而執行緒交互通訊則透過能使執行緒及XCores於硬體層交互作用之通道機制-XLink進行。這些介於實體世界及處理器引擎間的橋樑,為軟體設計者及硬體工程師提供了一個穩定而簡易的介面。

第一代XMOS SDS晶片之設計工具及工程樣品將於2008年上半年供應,並預計於之後的1-2季進行量產。