科技进步,一日千里,一转眼个人电脑市场的CPU速度竞赛已经堂堂迈入GHz大关,对消费者来说,相同的荷包预算可以买到愈来愈快的CPU,但对主机板的设计工程师来说,却是面临愈来愈大的挑战,特别是在CPU的电源供应设计上。

VRM是Intel公司制订的CPU电源需求规格,包括了VID的电压定义、CPU电压需求的稳态容忍误差与暂态容忍误差等等,因此从CPU电源设计的角度上来看,电力转换器的性能必须满足VRM的规范才算合格,而不同的CPU所需求的VRM版本也有不同。 VRM8.x的CPU在市场上已经是主流规格很久了,VRM9.0的CPU则是开始如雨后春笋般的出现,并有可能取代VRM8.x的CPU而成为市场主流,不过在尚未非常普及之前,其稳定性与性能表现都需要在大量生产后的实际验证才能证实。在此新旧规格交替之际,使用VRM9.0的控制IC会有复杂、高成本的问题,而VRM8.x的控制IC在市场上选择多、价格便宜、稳定性高,而且可以延续过去的设计经验,因此如何使用VRM8.x的PWM IC来设计满足VRM9.0 CPU的电源供应,成为相当有竞争力的解决方案。

CPU电源系统架构的演进

由于新一代CPU对电源的需求愈来愈多,也愈来愈苛,CPU的电源供应设计也面临更多的挑战;从过去CPU演进的趋势与特点可以发现,CPU的电源电压需求愈来愈低,而且在CPU追求速度狂飙的趋势之下,电流的需求也愈来愈大,这些特点都反映在CPU的电源设计上,而我们也可由此来了解一下电源系统架构的演进,(图一)画出了几种常见的架构。

早期的CPU电流需求不大,电源系统只要一颗LDO就可解决,然而LDO的缺点在于效率差,所损耗的能量在电流需求增加时也愈明显,且散热也是相当头疼的问题,因此切换式的电源设计开始成为主流。

要采用切换式的电源设计最简单的架构就是Buck架构,或是称为降压式转换器,由于设计简单,而且整个效率、性能表现都凌驾于前一代的LDO电源系统之上,因此立刻成为最为普遍广泛的设计。 Buck Converter的架构也成为未来CPU电源系统的基本架构,所有的新设计与技术都是以Buck为基础来进行改良的。

由传统的Buck Converter演进到Synchronous Buck架构,主要是基于效率的考量,其差异是将Buck中的飞轮二极体改为MOSFET,而从控制上的角度来看,这个MOSFET的切换动作恰好和原来的MOSFET形成互补,而效率提高的主要原理是要利用下臂MOSFET的导通压降低于原来采用二极体时的压降。不过原来的二极体并不见得一定要拿掉,因为在上下臂交替切换的休时时间(Dead Time)中,还是需要二极体来负责电流转移的工作,这个二极体可以用下臂MOSFET的Body Diode,但压降较大,如果有外加一个Schottky Diode,那么在休息时间的二极体压降损耗又可以再降低。

事实上从电力电子技术的角度来看,一旦Converter的架构确定了,系统性能的表现会受到选用元件特性相当大的影响,因此读者会发现电源设计的焦点会开始放在元件的选择之上,甚至元件的ESR、ESL以及寄生电容等平常不是很重要的参数,在CPU的电源系统设计上,反而成为整体性能表现,甚至于成败的重要关键。

当单纯Synchronous Buck架构也不敷使用时,Power Device的并联技术开始广泛的应用,包括MOSFET、Schottky Diode、电感、电容等。元件并联的优点主要有二,第一个是分担电流,因此元件的电流额定可以少一半,而元件上ESR所产生的损失也会少一半;第二个是元件的放置和线路的Layout会比较有弹性,这一点对电容器在电源系统中所扮演的角色更为重要,也对转换器的输出特性有显著的影响。

Multi-Phase技术则是对新一代CPU电源需求所提出的解决方案,基本的原理也是并联,不过不是功率元件的并联而是整个电源模组的并联。 Multi-Phase最大的优点除了使用多组电源模组分担负载电流之外,是利用不同电源模组间PWM信号的相位位移来达到降低输出涟波的目的,这个特性对于现在CPU的核心电压都低于2V以下来说是相当重要的,一方面可以更容易符合电压误差的规范,另一方面也可减少输出滤波器的大小。然而应用Multi-Phase的技术会使得控制系统变得复杂,而且牵涉到Current Sharing的问题,因此要采用这样的解决方案,会在成本上付出比较大的代价,至少在现阶段Multi-Phase的控制IC刚问世不久的时期内会是如此。

CPU电源设计架构选择

在面对目前需求大电流的CPU场合,大概有下列三种的电源设计选择:

使用一组Synchronous Buck架构,配合Power Device的并联使用

此架构是延续Synchronous Buck的架构,因此PWM IC与控制回路的架构也都相同,不需大幅地改版之前的设计,成本与过去类似。在电源转换的部份,利用MOSFET/Schottky元件的并联使用,可以有效的降低导通损失,并一起分担负载电流的大小。但是,随着电流需求的提高,元件的切换损失会成为主要的功率损失来源,在输出滤波器的部份,电感的并联也可降低因ESR造成的损失,输出电容器的ESR直接影响到负载调整率和暂态特性。在输出电压要求愈来愈低时,电源电路的布线也变得更为敏感,直接影响电源转换系统的性能。

使用Multiphase技术,采用Multiphase整合控制IC

这是目前这个产业中最新的解决方案,目前比较常见的设计是两个与三个Phase的设计。使用Multi-Phase技术的优点是输出电压与电流的涟波会衰减不少,因此在输出滤波器的设计上,元件的值会比单纯的Synchronous Buck小,这表示电容的成本可以节省,同时多组的电源模组也可达到分担负载电流的目的。但是在成本方面,采用Multi-Phase整合控制IC会比一般的Synchronous Buck的PWM IC贵上许多。

使用Multi-Phase技术,采用Synchronous Buck控制IC加上额外的电流控制回路

如果考虑到Multi-Phase整合控制IC的价格太高,但是又想引入Multi-Phase的技术,那么另外一个方式是从技术着手,可以Synchronous Buck的控制IC来作为个别电源转换模组的控制核心,然后再加上另外设计的电流控制回路来完成电流分配(Current Sharing)的功能。不过这样的设计对于工程师来说会是一个蛮大的挑战,尤其在电流控制回路与相位差的设计部份,完成的系统会比较复杂,而且元件和走线会占比较大的PCB面积。

对于上面的三种解决方案来说,第三种因为控制技术上过为复杂,因此即使成本上有优势,也不建议使用。第一种或第二种方案则是比较适当的选择,虽然使用Multi-Phase的整合控制晶片时所需的电容法拉值可以减少,不过在控制晶片的部份,价格会高出蛮多的,因此整体比较的结果,第一个方案会是比较经济实惠的方案,特别对于低价的电脑市场,这样的解决方案是更具有吸引力的。

部份读者可能会关心的是,从散热的观点来比较这两种方案的实用性;根据笔者的实测经验和资讯,两者在大电流(负载约40A)的工作条件下,使用Surface Mount的MOSFET,温度都会高达100oC左右,两者的温度差则大约差10oC左右(Multi-Phase较低)。这样的结果其实也是可以预测的到的,因为就MOSFET来说工作电流还是那么大,因此导通损失是差不多的,而个别MOSFET的切换频率其实也差不多,因此切换损失也是差不多,所以整个MOSFET上所消耗的功率也是接近的。

不过这样的温度其实还是有降低的空间,举例来说,如果MOSFET是采用TO220包装并加上散热片,那么对散热的效果会大有帮助,如果再加上风扇的协助导热,MOSFET的温度会降低更多。事实上,从电力电子技术的角度来看,在45A这样的电流应用之下,采用Hard Switching技术架构的Buck Converter,要完全靠PCB的铜箔来散热已经是愈来愈不可能的了,如果不引入Soft Switching的技术,MOSFET加散热片或加上额外的风扇来处理散热的问题会是必然的趋势。

VRM 8.x到VRM9.0的ID转换

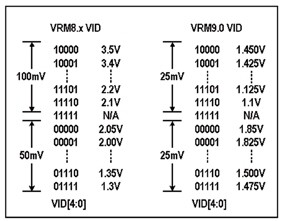

除了考虑大电流的需求必须在电力转换架构上做改变之外,在此VRM8.x与VRM9.0的规格交替之际,VID所定义的电压范围不同也造成了沿用既有VRM8.x规格的PWM IC至VRM9.0系统上的限制,但是透过控制IC外部回授电路的调整,VRM8.x的VID设定可以调整到符合VRM9.0的VID电压设定。在介绍实际的电路应用设计之前,我们先来比较一下VRM8.x和VRM9.0的电压设定值的差别到底在哪里,透过下面(图二)中的图示会比较容易了解。

| 《图二 VRM8.x与VRM9.0的VID对应电压设定比较》 |

|

从图中可以清楚的比较出来VRM 8.x和VRM9.0的的VID电压对应值的差异,主要包括了两个部份:

1.定义的电压范围不同。 VRM 8.x是从1.3V~3.5V,而VRM9.0则是从1.1V~1.85V

2.电压步阶(Voltage Step)不同。 VRM 8.x的步阶在VID4=1时是100mV,在VID4=0时是50mV(注:VID4即为五个VID位元的Msb),而对VRM9.0而言,在所有的范围内都是25mV。

了解VRM8.x和VRM9.0的VID差异之后,接下来要看的是如何做简单的线性转换,(图三)简单的画出了转换的流程,参考这个图会比较清楚转换的关系。

1.首先看VRM8.x的VID对应电压表的部份,我们会发现在VID4=1时,定义电压的范围是2.1V~3.5V,这个部份的电压在VRM9.0中是完全没有用到的,因此这个部份可以直接删除。对VRM8.x的PWM IC而言,VID4可以直接接地,此时VID电压表只包含了16个值,由VID0~VID3来定义。

2.在16个电压值的部份,电压步阶都是50mV,为了要达到VRM9.0的电压步阶都是25mV的目的,我们可以加入一个新的VID5,用来定义这些电压值是否在加上25mV的步阶。如图二中STEP 1的部份所示,当VID5=1时,原来的电压值保持不变(由VID0~3)定义,当VID5=0时,原来的时再加上25mV。因此我们又可以得到5个VID定义的32个电压值,而且是25mV的电压步阶。

3.如此一来,这些电压值的范围为1.3V~2.075V,和VRM9.0的电压范围差异只剩下一个Offset,这个Offset的值是225mV(2.075-1.85=0.225),接下来就是把电压表中的每一个值都减掉225mV就可以了,如图二中的STEP 2所示,因此我们可以得到完全吻合VRM9.0的电压设定。唯一的例外是11111在VRM9.0中是定义为「No CPU」,而我们由VRM8.x转换过来的VID电压表中是1.075V。

4.最后还有一件事要做的就是把VID0~3与VID5重新排序,以符合VRM9.0的VID顺序。原来的VID0~3更名为VID1~4,而VID5更名为VID0,这样的结果就会和VRM9.0的VID顺序吻合了。

电路上的实现

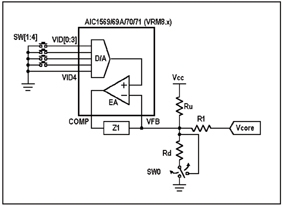

在电路上要实现的功能主要包括了「+25mV」与「-225mV」两个部份,要如何做呢?我们可以从Buck Converter控制回路中的误差放大器(Error Amplifer)动作原理来看。通常在PWM IC中的误差放大器一支输入接脚是参考电压(Reference Voltage),也就是前面提到由VID设定,经过DAC(Digital/Analog Converter)转换的参考电压,另一只脚则是回授电压的输入,如(图四)所示。

对误差放大器来说,在控制系统中所扮演的角色是要维持两支输入接脚的电压相同,因此只要适当的调整回授的电压比例就可以达到调整输出电压的目的。 (图五)说明了调整回授电压的两种方式。

在图五中,R1是原来回授控制器(由误差控制器和Z1, Z2组成)中的Z1,我们只要另外加上一个电阻,一端连接VFB接脚,另一端连接至接地点或是一个大于Vcore的电压源,就可以利用分压的原理达到调整输出电压的目的。以接一个电阻下地的例子来说,Vcore一定会大于VFB,因此我们可以出在R1上所需的25mV电压差。同样的,在接一个电阻到电压源的部份,Vcore一定是小于VFB,因此也可以设计出225mV的电压差。两个电阻Rd和Ru的值算出来后,利用重叠原理,就可以完成电路的实现。详细的阻值设计和分析可以参考本文最后之参考文章[1]。最后整个电路的架构如(图六)所示。

| 《图六 VRM8.x VID转换至VRM9.0 VID电路架构》 |

|

如图六所示,Ru电阻的效果是将Vcore电压减少225mV,而Rd则是根据SW0的选择来决定是否将Vcore提高25mV,因此整体而言,要完成VID的转换只需多加上两个电阻和一个DIP Switch,就成本上来说的确是非常经济实惠的。不过这样的应用也有一些小问题是需要注意到的,主要是在设计Ru和Rd的值时,会受到VID设定的影响,因此在不同的电压设定时会有一些误差,不过这个误差还不至于差到25mV的一半,因此仍然是可以接受的解决方案。如果要深究这个问题,其实还是有办法解决的,因为其实这样的VID转换原理是在控制R1电阻上的电压降,而R1的端电压差是由Vcc/Gnd与Vcore决定的,因为Vcore改变,影响了R1上的电流大小,所以才会造成R1端电压差的变化,因此要完整解决这个问题的方法,可以采用在VFB注入电流,并控制此电流源的大小,这样R1电阻上的电压差就不会受到Vcore的影响,单纯地由注入电流的大小和R1的阻值来决定。这个电流源的设计只需一个LM358和几个电阻就可以完成[2]。

结论

应用VRM8.x的PWM控制IC来满足VRM9.0的CPU需求充满了许多不同的挑战,包括除了电力转换器的架构必须加强以满足更大的电流需求外,在功率元件的选取、驱动电路的设计等方面都需重新检讨,以确保电源的供应满足VRM9.0的需求。然而其中最令人头疼的还是VID的转换问题,因为大部份VRM8.x PWM IC的DAC是内建于IC之中,而且DAC输出的Vref信号也无法提供外部电路使用,因此只能从回授控制系统来着手。然而这些问题在沛亨半导体都已经有提供完整的Total Solutions,包括高达45A的High Current Demo Board、Application Note与完整的技术支援,有兴趣的读者可以直接与该公司联络。

[1]Silvan Ho, "A novel, cost-effective technique for converting VRM8.x VID to VRM9.0 compatible VID", Application Note AN00-SR03EN, Analog Integrations Corporation.

[2]详细应用技术资料可与沛亨半导体(AIC)产品应用课工程师联络,电话(03)5772500 ext881,地址:新竹科学工业园区工业东九路9号4F。