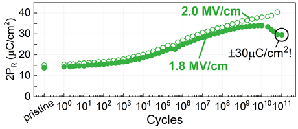

於本周舉行的2022年IEEE國際電子會議(IEDM)上,比利時微電子研究中心(imec)展示了一款摻雜鑭(La)元素的氧化鉿鋯(HZO)電容器,成功取得1011次循環操作與更佳的電滯曲線(電場為1.8MV/cm時,殘留極化值達到30μC/cm2),並減緩了喚醒效應。此次能夠實現鐵電電容的多項性能升級,關鍵在於介面氧化工程技術。這項鐵電電容技術具備高性能、微縮能力與CMOS相容性,將是實現新一代嵌入式與獨立式鐵電隨機存取記憶體(FeRAM)應用的關鍵。

|

| 不同鐵電電容與氮化鈦(TiN)電極的元件耐久性測量(殘留極化值與循環次數的比較)。綠色曲線是重點,該元件採用三層(TriLayer)堆疊,包含一層二氧化鈦(TiO2)種子層與五氧化二鈮(Nb2O5)覆蓋層。 |

鐵電記憶體(FeRAM)是一種非揮發性記憶體,可望作為新興的嵌入式或儲存級記憶體,滿足高速DRAM(讀取時間小於10奈秒)與高密度NAND快取記憶體未能填補的市場需求。與DRAM結構相似,鐵電記憶體也是由1個電晶體與1個電容組成;為了實現非揮發性,以鐵電材料取代介電材料作為電容。鐵電材料包含兩種極化狀態(+P與-P),藉由施加外部電場就能轉換。過去幾年,氧化鉿鋯(HZO)因為可用於CMOS製程並具備10奈米以下的微縮潛能,成為備受矚目的鐵電材料。

為了製成嵌入式記憶體或儲存級記憶體,必須具備幾項元件特性。理想情況下,鐵電記憶體的電容具備1012次以上的超耐久循環,同時,在生命週期內殘留極化量(2PR)達到30-40μC/cm2。但到目前為止,仍無元件能同時實現這兩者,因為鐵電材料的電容面臨了延遲喚醒(最初的殘留極化量低)與快速疲勞(殘留極化量快速下降)的問題。

比利時微電子研究中心(imec)鐵電元件研究計畫主持人Jan Van Houdt說明:「利用介面氧化工程技術,以及在鑭(La)摻雜氧化鉿鋯(HZO)元件層各導入一層1nm二氧化鈦(TiO2)種子層與一層2nm五氧化二鈮(Nb2O5)覆蓋層,我們成功開發了同時具備優良耐久性(1011次循環操作)與殘留極化量(在施加1.8MV/cm外部電場的情況下,殘留極化量達到30μC/cm2)的元件,而且起始操作階段的極化性也不錯。」

「經過初步了解,該元件與Nb2O5覆蓋層的接面能促進HZO材料轉換至所需的斜方晶相,也就是鐵電相,做法是在HZO層注入氧離子,TiO2層則有利於製出(002)晶體,進一步提高殘留極化的初始值。」他說道。另一種做法是採用不同的前驅物來沉積HZO層,結果創下了歷史新高的極化值,電場為3MV/cm的情況下達到66.5μC/cm2,但循環操作只有106次。“

Jan Van Houdt接著表示:「現在有了這項高性能、與CMOS相容且可微縮化的鐵電電容技術,我們就能步入下個振奮人心的新階段,就是導入原子層沉積技術,將原先採用平面結構的鐵電電容3D化。如此一來就能實現儲存密度的升級,將鐵電記憶體推向市場, 製成新一代嵌入式或獨立式記憶體。」