本文探讨如何在雪崩运作条件下评估SiC MOSFET的鲁棒性。 MOSFET功率转换器,特别是电动汽车驱动马达功率转换器,需要能够耐受以前的运作条件。元件在续流导通期间出现的失效或闸极驱动命令讯号错误,确实会致使转换器功率开关二极体在雪崩条件下运作。因此,本文透过模拟雪崩事件,进行非钳位元感性负载开关测试,并使用不同的SiC MOSFET元件,依照不同的测试条件,评估技术的失效能量和鲁棒性。

引言

效能和可靠性是所有电子功率转换器必备的主要特性。在与人类社会活动和生态环境保护相关的应用领域,例如,交通、工业、能源转换等,标准矽基功率开关已被SiC MOSFET取代,因为 SiC MOSFET在电流密度/晶片面积、击穿电压、开关频率、工作温度方面表现更出色,可缩减功率转换器的体积和尺寸,同时提升效能[1],[2]。

采用最新一代SiC MOSFET设计功率转换器还必须考量元件的可靠性和鲁棒性,不应该让异常失效现象破坏系统的整体安全性[3],[4]。短路和雪崩是可能导致电源转换器开关严重失效的异常事件[5-6]。

短路事件可能是错误和失控的工作条件引起的,例如,元件开关顺序命令出错。当漏源电压VDS超过击穿电压额定值时,会发生雪崩事件[7]。

对于dvDS/dt和diD/dt变化率很高的应用,在开关瞬变期间,VDS可能会超过击穿电压额定值。高瞬变率结合转换器布局固有的寄生电感,将会产生电压尖峰,在极端情况下,导致雪崩事件发生[7],[14],[16]。 SiC MOSFET可能会出现这些运作条件,离散元件的dvDS/dt可能轻松超过100V/ns,而diD/dt则超过10A/ns [1],[21]。

另一方面,马达功率转换器,例如,电动汽车的驱动马达逆变器、工业伺服马达等,这些负载具有典型的电感特性,要求功率开关还必须兼具续流二极体的功能[18]。因此,在二极体关断时,其余元件将传导负载电流,进行非钳位元感性负载开关UIS操作,运作于雪崩状态是无法避免的[13]。在这种雪崩期间,除过电压非常高之外,高耗散能量也是一个需要考虑的重要问题,因为元件必须耐受异常的电压和电流值。

采用失效检测演算法和保护系统,配合同样具备「可靠性」标准的转换器设计方法,是必要的[20]。但是,除了安全保护和最佳设计规则外,功率开关还必须稳固,即具有「鲁棒性」,才能耐受某种程度的异常运作条件,因为即便超快速侦测演算法和保护系统也无法立即发挥作用[19]。 SiC MOSFET的雪崩问题已成为一个重要的专题,由于该技术尚未完全成熟,因此需要进行专门的研究[7]-[13]。

本文的目的是分析SiC MOSFET在雪崩工作条件下的鲁棒性。为了验证鲁棒性分析结果,做了许多实验。最后介绍元件在不同的UIS测试条件的鲁棒性。

雪崩事件

雪崩事件基本上是在元件达到击穿电压时才会发生。在正常工作条件下,凡是设置或要求高开关频率的应用都会发生这种现象。

以半桥转换器的应用为例,让我们详细解释一下雪崩现象。

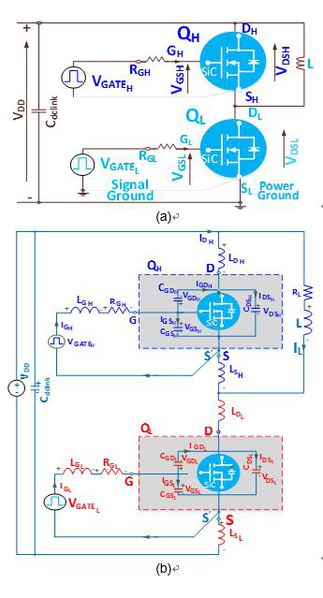

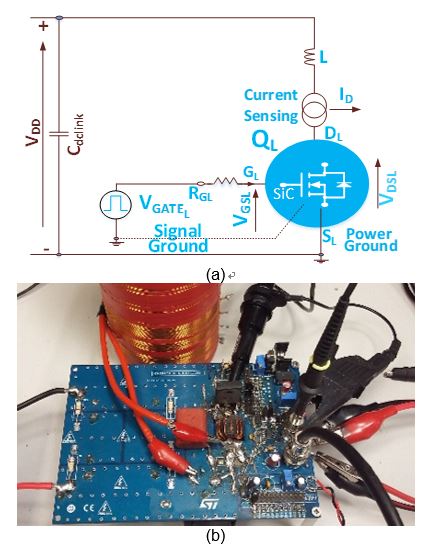

图1(a)是一个简化的半桥转换器电路原理图,电路中有两个SiC MOSFET开关,分别用QH和QL表示,除开关外,还有一个感性负载;图1(b)是上面电路的等效电路图,最重要的部分是主要寄生元件,特别是代表电源回路等效寄生电感的LDH,LSH,LDL和LSL,电源回路是指连接+ DC电路(VDD)与QH漏极,QH源极至QL漏极,QL源极至-DC电路的电源轨。

此外,LGH,LGL是QH和QL的闸极-源极路径讯号回路的等效寄生电感。考量到HiP247封装离散元件有三或四个引线,上面的寄生电感中包含SiC MOSFET焊线和引线的寄生电感,详细资讯参见[15],[16]。同样重要的是,还要考量SiC MOSFET的寄生电容CGS,CDS和CGD,这些参数是漏极-源极电压VDS的函数[21]。

不难理解在下面两个案例的极端运作条件期间产生的电压尖峰:

1.有源元件导通,无源元件的体二极体关断

2.有源元件关断,无源元件的体二极体导通

用1200V,25mΩ,HIP247-4L封装的SiC MOSFET离散元件,按照图1的方案做实验测试,描述瞬变在什么情况下被定义为极端作业条件。为简单起见,将QL视为有源元件,它由适合的闸极驱动器电路控制;QH是无源元件,用作续流二极体,并且通常在相关终端施加-5V的恒定负闸极-源极电压。

| 图1 : 半桥转换器桥臂:(a)简化框图,(b)包括主要寄生元件的等效电路。 |

|

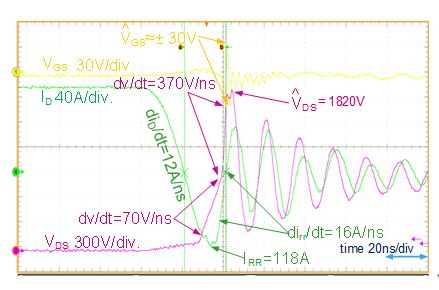

透过分析图2的实验结果,可以了解案例1的极端作业条件。

| 图2 : 在850V, 130A,QH 体二极体关断时,VGS, ID 和VDS的典型波形。 |

|

本节重点介绍在QL导通时QH体二极体的「反向恢复」过程。测试条件是175°C,VDD=850V, ID=130A。 SiC MOSFET的反向恢复过程是一个重要的课题,许多人都在研究这种现象[17],[18]。软恢复和硬复原模式受载流子寿命、掺杂分布、裸片面积等因素影响。从应用角度来看,反向恢复特性主要与正向电流大小ID及其变化率diD/dt和作业温度有关。

图2显示了变化速率12A/ns的ID引起之QH体二极体硬恢复特性。由于结耗尽非常快,漏极-源极电压VDS以最快的速度上升。在diD/dt 和 dirr/dt与寄生电感的综合作用下,尖峰电压现象严重,并且在VDS波形上看到振荡行为。另外,VGS波形出现明显振荡,应钳制该电压,以避免杂散导通[16]。

快速恢复用于描述恢复的效果,概念定义详见文献[17]。

透过优化转换器电路板布局,将寄生电感降至非常低,可以限制在电流变化率非常高的关断期间产生的电压尖峰,从而最大程度地利用SiC MOSFET的性能。

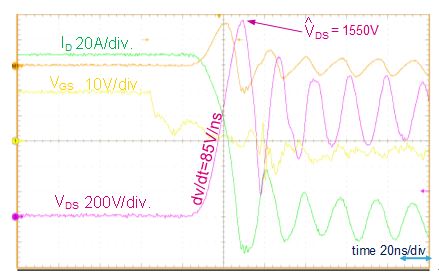

图3的实验测试结果解释了案例2的极端运作条件。图中所示是在室温(25°C),850V,130A条件下QL「关断」时的相关参数波形。因为元件采用HIP247-4L封装,3.3?的闸极电阻Rg加速了关断瞬变,并且VDS的峰值非常高(约1550V)。

| 图3 : 在850V, 130A条件下关断QL,VGS, ID, VDS 和 Poff的典型波形。 |

|

透过进一步降低Rg阻值提升关断速度,将会引发雪崩事件,不过,在本实验报告中没有达到雪崩状态。

但是,除极端工作条件外,元件失效也会导致雪崩事件[4]。

以前文提到的图1半桥转换器为例,当QH续流二极体失效,致使元件关断时,负载电流必须在关断瞬变期间流经互补元件QL,这个过程被称为非钳位元感性负载开关UIS。在这个事件期间,元件必须承受某种程度的能量,直到达到QL击穿极限值为止。

这种失效机制与临界温度和热量产生有关。 SiC MOSFET没有矽基元件上发现的其它失效模式,例如,BJT闩锁[10]。在UIS条件下的雪崩能量测试结果被用于定义SiC MOSFET的鲁棒性。

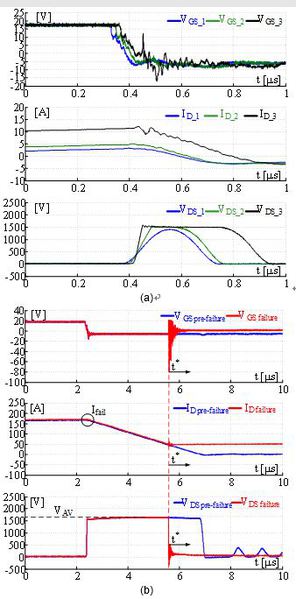

图4(a)和图4(b)是SiC MOSFET的UIS测试结果。这些测试是在图1无QH的配置中做的,测试条件是VDD=100V, VGS=-5/18V, RGL=4,7?, L=50H, Tc=25°C,下一章将详细分析这样选择的原因。

图4(a)所示是前三次脉冲测试。 QL正在传导电流,在第一个脉冲时关断,如图中蓝色的VGS,VDS和ID的波形所示,有过电压产生,VDS略低于1500V,但元件没有雪崩。在增加脉冲周期后,如图中绿色波形所示,电流ID达到5A,元件开始承受雪崩电压。再重复做一次UIS测试,如黑色波形所示,电流值变大,但由于负载电感器较小,直到电流值非常大时才达到失效能量。

| 图4 : UIS实验,(a)雪崩过程开始时的波形;(b)施加最後两个脉冲时的波形。 |

|

图4(b)所示是最后一种情况的测试结果。蓝色波形是在一系列单脉冲后,元件失效前倒数第二个脉冲产生的波形,从图中可以看到,元件能够处理关断瞬变,耐受根据下面的雪崩能量公式(1)算出的约0,7J雪崩能量,最大漏极电流为170A,雪崩电压平均值为1668V。

EAV = 1/2 LI2fail VAV / VAV-Vnn (1)

红色波形是在施加最后一个脉冲获得的失效波形,这时元件不再能够耐受雪崩能量,并且在t*时刻发生失效,漏极电流开始骤然增加。

鲁棒性评估和雪崩测试

我们使用三组1200V SiC MOSFE进行UIS测试,表1详列出这三组元件的主要资料。

5(a)所示是测试等效电路图,5(b)所示是相关实验装置。 QL是待测元件(DUT),测试目标是分析DUT的关断特性。

表1:SiC MOSFET规格

|

SiC MOSFET

|

VBD [V]

|

RDS(on)[m?]

|

ID@(25°) [A]

|

|

D1

|

1200

|

83 @ VGS=18V, ID=20A

|

20

|

|

D2

|

1200

|

30 @ VGS=18V, ID=60A

|

70

|

|

D3

|

1200

|

20 @ VGS=18V, ID=100A

|

100

|

| 图5 : UIS实验装置: (a)等效电路, (b) 实验台 |

|

设定A,B,C三种测试条件;施加周期递增的单脉冲序列,直到待测元件失效为止。

VDD=100V, VGS=-5/18V

A. vs rgl = 4,7?,10?,47.,在l = 50uh,tc = 25°C

B. VS L = 50UH,1MH,RGL = 4,7?,TC = 25°C

C. VS TC = 25°C,90°C,200°C,在L = 50UH,RGL = 4,7?

为了便于统计,从D1,D2和D3三组元件中分别抽出五个样品,按照每种测试条件各做一次UIS实验,测量和计算失效电流和失效能量,参见图6,图7和图8。

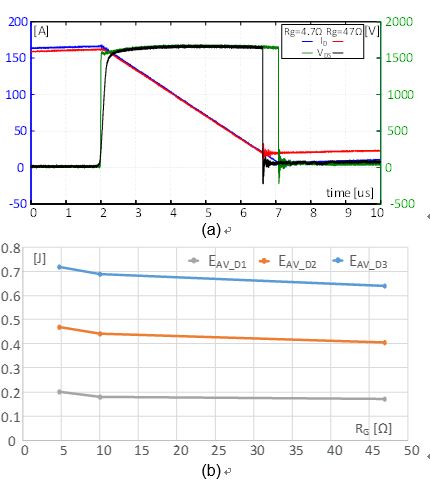

图6(a)所示是从SiC MOSFET D3中抽出的一个典型元件,按照测试条件「A」做UIS测试的VDS和ID失效波形。

| 图6 : UIS对RG最终测试结果:(a) 一个D3样品的VDS和ID典型值;(b)平均失效能量EAV。 |

|

为了清楚起见,只给出了RG =4.7Ω和47Ω两种情况的波形。我们观察到,失效电流不受RGL的影响。图6(b)显示了D1,D2和D3三组的平均EAV。

注意到EAV失效能量略有降低,可忽略不计,因此,可以得出结论,在UIS测试条件下,这些SiC MOSFET的鲁棒性与RG无关。

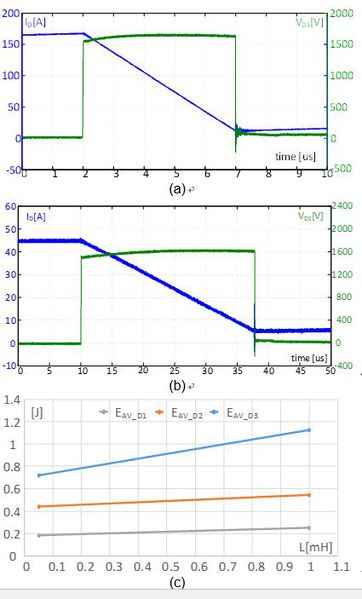

图7(a)和(b)所示是按照测试条件B,在L=50H 和1mH时,各做一次UIS测试的失效波形,为简单起见,只从SiC MOSFET D3中抽取一个典型样品做实验。

在提高负载电感后,电感器储存的能量增加,因此,失效电流减小。

| 图7 : UIS对L最终测试结果(a)在L=50 H时, D3样品的VDS和ID典型值 (b)在L=1mH时, D3样品的VDS和ID典型值(c)平均失效能量EAV. |

|

图7(c)显示了D1,D2和D3的平均EAV与L的关系,可以观察到,元件D3的失效能量EAV随着负载电感提高而显著提高,而D1和D2的EAV则略有增加。透过分析图8可以发现这种行为特性的原因。图8是根据等式(2)计算出来的结温Tj的分布图:

Tj=T0+PAVZth (2)

其中:T0是起始温度,PAV是平均脉冲功率,Zth是晶片封装热阻,本次实验用的是不带散热器的TO247-3L封装。

电感器储存能量的大小与电感值有关,储存能量将被施加到裸晶片上,转换成热能被耗散掉。

如图7(a)所示,低电感值会导致非常大的热瞬变,这是因为电流在几微秒内就达到了非常高的数值,如图7(a)所示,因此,结温在UIS期间上升非常快,但裸片没有够的时间散掉热量。反之,在高电感值的情况下,电流值较低,如图7(b)所示,并且裸片有足够的时间散掉热量,因此,温度上升平稳。

这个实验结果解释了为什么被测元件D3的EAV随负载电感提高而显著增加的原因,另外,它的裸片面积比SiC MOSFET D1和D2都大。

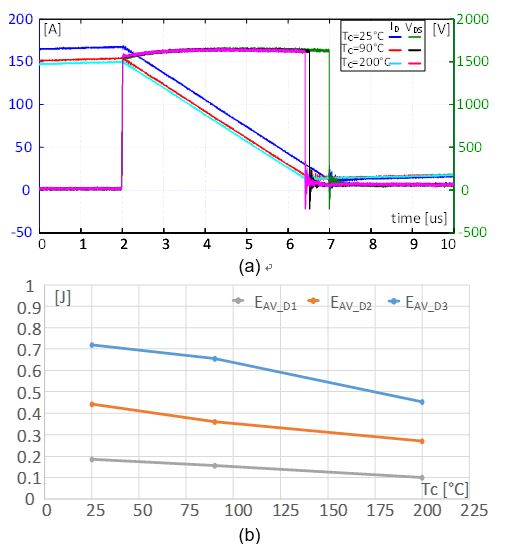

最后,在图9中报告了测试条件C的UIS测试结果,测试条件C是封装温度的函数,用热电偶测量封装温度数值。

图9(a)所示是D3在Tc=25°C,90℃和200℃三个不同温度时的VDS和ID波形。不出所料,D1,D2和D3三条线的趋势相似,工作温度越高,引起元件失效的EAV就越低,图9(b)。

| 图9 : UIS对Tc的最终测试结果;(a)D3样品在不同的Tc时的VDS和ID典型值;(b)平均失效能量EAV 对TC曲线 |

|

结论

本文探讨了在SiC MOSFET应用中需要考虑的可能致使功率元件处于雪崩状态的工作条件。为了评估SiC MOSFET的鲁棒性,本文透过实验测试评估了雪崩能量,最后还用三款特性不同的SiC MOSFET做对比测试,定义导致元件失效的最大雪崩能量。雪崩能量与晶片面积成正比,并且是闸极电阻、负载电感和外壳温度的函数。

这种在离散元件上进行的雪崩耐量分析,引起使用电源模组开发应用的设计人员的高度关注,因为电源模组是由许多并联晶片组成,这些晶片的鲁棒性需要高度一致,必须进行专门的测试分析。此外,对于特定的应用,例如,汽车应用,评估雪崩条件下的鲁棒性,可以考虑使用单脉冲雪崩测试和重复雪崩测试方法。这是一个重点课题,将是近期评估活动的目标。

(本文作者Salvatore La Mantia1、Mario Pulvirenti2、Angelo G. Sciacca2、Massimo Nania2

任职于1 STMicroelectronics, GmbH Germany和2 STMicroelectronics, Italy)

参考文献

[1] f。

[2] s。

[3] b。

[4] a。

[5] b。

[6] f。

[7] a。

[8] m。

[9] i。

[10] n。

[11] j。

[12] j。

[13] m。

[14] h。

[15] m。

[16] m。

[17] j。

[18] r。

[19] y。

[20] r。

[21] https://www.st.com/resource/en/datasheet/scth90n65g2v-7.pdf