赛灵思All Programmable元件与工具支援从二进位到双精度浮点在内的多种资料类型。相较于浮点运算,执行于定点运算的设计拥有更高的效能,由于定点运算仅需消耗少许的资源和功耗。当设计迁移到定点时,功耗与占用面积缩减一半也不稀奇。

相较于浮点,定点资料类型的优势,包括:

‧ 逻辑资源使用减少

‧ 功耗降低

‧ 材料成本降低

‧ 延迟缩短

支援的资料类型

赛灵思所有元件均支援需要浮点资料类型所提供的动态范围之客户,并提供高达7.3TFLOP的单精度浮点DSP效能。

赛灵思工具套件提供浮点支援。 Vivado高阶合成技术(HLS)和DSP系统产生器(System Generator)本身均支援可变的浮点精度,包括半精度(FP16)、单精度(FP32)及双精度(FP64);系统产生器亦支援具较大弹性的客制化精度。这些工具本身也支援可变定点资料类型。

表1:赛灵思工具支援浮点与定点资料类型 (注1-2)

赛灵思工具 |

FP16 |

FP32 |

FP64 |

客制化FP |

定点 |

Vivado HLS |

Y |

Y |

Y |

N |

Y |

DSP系统产生器 |

Y(1) |

Y |

Y |

Y |

Y |

浮点运算IP |

Y |

Y |

Y |

Y |

Y(2) |

赛灵思元件和工具提供的可变精度资料类型,可提供客户简单且弹性的解决方案,来调整并适应业界的趋势变化,例如图像分类只需要INT8或更低的定点运算,就能保持可接受的推论精度。

用于高运算密集工作负载的GPU等其他元件,传统上其结构仅用于有效支援单精度浮点,而这些厂商现已开始重新设计产品,来因应趋势的变化。然而,赛灵思的可扩展架构让客户能扩展单讯号处理链的精度,以满足业界日新月异的需求。

客户在选择运用浮点还是定点讯号处理链时,必须在功耗、成本、生产力与精度之间仔细权衡。

赛灵思弹性的DSP48E2分割(Slice)可在进行重要的DSP运算时,适用于所有资料类型。当运行新定点设计或针对某些应用将现有设计从浮点转换成定点(当转换为适用选项)时,DSP分割与赛灵思工具集相结合能带来巨大优势与弹性。

对于采用C/C++语言设计的客户,赛灵思提供Vivado HLS并支援任意精度定点资料类型,使客户能轻松地采用定点进行设计,或将现有的C/C++设计转换为定点。

浮点转换为定点的优势

对目前几乎所有的设计来说,将功耗最小化是首要目标,且大多数的应用产品必须先满足严格的功耗和散热范围需求才能投产。

相较于较低精度,目前普遍接受的原则是在浮点内的设计会导致较高的功耗。对FPGA来说也一样,其中的浮点DSP模块在FPGA中已被强化,且客户必须使用提供的DSP资源与其它FPGA资源来运行软解决方案。浮点方案与同等的定点解决方案相比,会使用较多FPGA资源,且当资源使用增加,功耗则随之增大,最终会提高设计运行的总成本。

将浮点设计转换为定点设计能透过以下方法,来满足具挑战性的规范:

‧ 减少FPGA资源

。使用定点资料类型时,需较少的DSP48E2、查表(LUT)与正反器。

。储存定点数所需的记忆体容量更小。

‧ 降低功耗

。减少FPGA资源利用自然会降低功耗。

‧ 降低材料成本

。设计人员能在相同成本内运用附加的可用资源,为其应用获得额外功能。

。资源的节约能大幅提升FPGA的运算能力,提升的运算能力能让许多应用受益,例如机器学习DNN。

。资源的节省也许能缩小设计所需的元件尺寸。

‧ 降低延迟

。运行FIR时减少所占用的资源,尤其是DSP48E2分割,能降低定点设计的延迟。

‧ 相近的效能和精度

。对于不需要用浮点来达到动态范围的设计与应用,定点方案能提供相近的结果与精度,在某些情况下,结果甚至更好。

过去由于缺乏工具支援,因此难以将设计从浮点转换为定点。对于选用赛灵思All Programmable元件的C/C++开发人员来说,使用Vivado HLS可减少转换过程中的挑战。

这种转换能带来许多优势,因此在适用情况下应认真考虑,尤其是不需要利用浮点来达到动态范围与浮点精度的设计,以及预期内少量的精度损失不会导致部署后应用效能降低。

实例:将浮点FIR滤波器转换为定点

Vivado HLS中简单的FIR滤波器设计可用来展示当浮点FIR设计转换为定点设计时,如何减少所用资源和功耗,并达到相近的结果精度。

单精度浮点FIR

在C++ FIR函数代码中,顶层函数在FIR.h标头档(header file)中找到的CFir类别(class CFir)的实例化。

#inclue“for.h”

// Top-level function with class instantiated

fp_acc_t fp_FIR(fp_data_t x) {

#pragma HLS PIPELINE

static CFir fir1;

return fir1(x);

}

CFir类别是主要的FIR演算法,在标头档中被定义为FIR.h

// FIR main algorithm

template

acc_T CFir::operator()(data_T x) {

//caller uses #pragma HLS PIPELINE which makes this function pipelined as needed.

#pragma HLS ARRAY_PARTITION variable=c complete dim=1

#pragma HLS ARRAY_PARTITION variable=shift_reg complete

dim=1

int i;

acc_T acc = 0;

data_T m;

loop: for (i = N-1; i >= 0; i--) {

if (i == 0) {

m = x;

shift_reg[0] = x;

} else {

m = shift_reg[i-1];

if (i != (N-1)) {

shift_reg[i] = shift_reg[i - 1]; }

}

}

acc += m * c[i];

}

return acc;

}

此函数包含重要的ARRAY_PARTITION编译指示,以确保设计的所有运行方案都是II=1(迭代区间为1),而PIPELINE编译指示也被应用于顶层函数调用。

这些编译指示、平行产品运行及用于执行累加的加法树,无论任何资料类型,都能确保整个FIR函数维持最低延迟,并保持II = 1。

在fp_FIR函数中,fp_coef_t、fp_data_t和fp_acc_t都被定义为浮点类型,即C++原生的单精度浮点资料类型。

// float

typedef float fp_coef_t;

typedef float fp_data_t;

typedef float fp_acc_t;

通过标头档中的include指令加载滤波器系数。

template

const coef_T CFir::c[] = {

#include "FIR_fp.inc"

};

用系数创建一个对称的FIR滤波器,但在本例中,未使用DSP48E2分割中的预加器,若使用预加器,则能达到更高效率。

以下是针对85-tap FIR滤波器在C合成及在Vivado HLS中执行,并采用XCVU9P-2FLGB2104元件上的400MHz时脉(2.5ns 时脉周期)所得到的结果。详见表2。

表2:单精度浮点FIR运行后的结果

单精度浮点(FP32) |

最大频率(FMAX) |

500MHz |

延迟(时脉周期) |

91 |

迭代区间(II) |

1 |

DSP48E2 |

423 |

查表(LUT) |

23,101 |

本例中,需要423个DSP48E2及约23,000个查表来运行单精度浮点FIR,运行结果显示延迟为91个时脉周期,最大频率(FMAX)为500MHz(远高于目标400MHz)。

转换到定点FIR滤波器

为了达到最高DSP效率,浮点到定点的转换必须考虑DSP分割的汇流排宽度,即27x18位元乘法器和48位元累加器。若进一步将汇流排宽度缩减至设计允许的最小值,能在资源与功耗上获得最大的回馈。

针对此FIR滤波器实例,定义以下定点资料类型以匹配DSP48E2分割中的汇流排大小,即18位元系数中1个整数位元和17个小数位元;27位元资料中15个整数位元和12个小数位元;以及48位元累加器中19个整数位元和29个小数位元。

// fixed points

#include

typedef ap_fixed<18,1> fx_coef_t;

typedef ap_fixed<27,15> fx_data_t;

typedef ap_fixed<48,19> fx_acc_t;

要使用Vivado HLS原有的ap_fixed资料类型,必须包含ap_fixed.h标头档,以定义任意定点资料类型。

采用400MHz时脉(2.5ns时脉周期)和XCVU9P-2FLGB2104元件,其C合成与运行定点FIR设计后所产生的结果,如下表3所示。

表3:比较两种设计运行后的结果

? |

单精度浮点 |

定点 |

定点优势 |

FMAX

(运行后) |

500MHz |

580MHz |

提高16% |

延迟 |

91 |

12 |

降低约7.5倍 |

迭代区间(II) |

1 |

1 |

- |

DSP48E2 |

423 |

85 |

DSP效率提高5倍 |

查表(LUT) |

23,106 |

1,973 |

逻辑效率提升11倍 |

正如结果所显示,当重视延迟与FPGA资源利用率时,可获得明显的改善。

在UltraScale架构中,可将多个DSP48E2分割串联,以支援更高的汇流排宽度。采用串联DSP48E2分割的定点设计,与浮点方案相比仍可显著减少资源使用与功耗。

比较滤波器精度

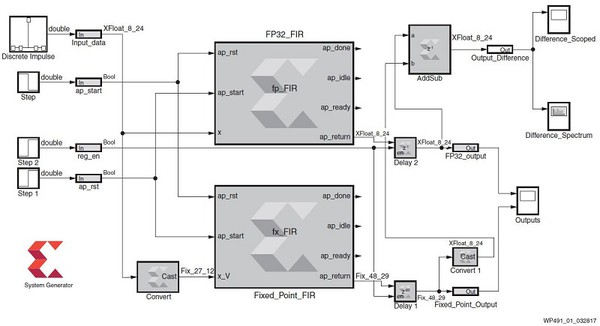

在DSP系统产生器中,使用来自赛灵思模组集的Vivado HLS模块,能在MATLAB/Simulink环境中,针对两种FIR滤波器的运行方案进行比较。如图1所示。

| 图1 : DSP系统产生器模型━使用两种HLS解决方案进行分析 |

|

系统产生器模型由两个Vivado HLS模块所组成,其配置包含来自Vivado HLS的单精度浮点(FP32)和定点FIR解决方案。两个模块具有相同的输入和离散脉冲讯号,然后在Simulink示波器上比较每一个FIR输出。如图2所示。

为了方便比较,有必要延迟定点结果,以按照两种解决方案之间的延迟差进行比对。

正如预期,两种FIR滤波器产生的结果几乎相同,且差异很小。

为进一步分析讯号,将两个输出相减,如图3的光谱分析所示,若讯号在 -100dBm至 -160dBm范围内,其精度损失非常小。

关键优势

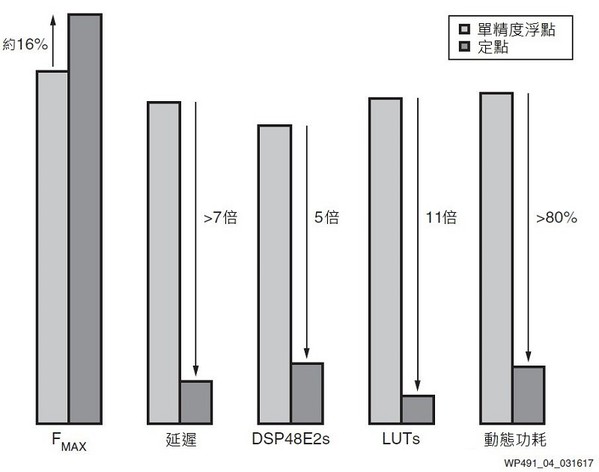

当把原始单精度浮点FIR滤波器与转换后定点FIR滤波器的结果进行比较时,发现定点设计不仅减少了资源使用与延迟,同时还能保持甚至改善设计的最大频率(FMAX)。如图4所示。

| 图4 : 定点━效能相近,并减少延迟、资源使用和功耗 |

|

大幅减少FPGA资源的使用

本例中的定点FIR比原始浮点FIR小五倍以上。

精选出的汇流排宽度是为了优化映射到硬体中的DSP48E2分割。这允许每个相乘都在一个DSP48E2分割中完成,并与每个85系数平行,让DSP48E2分割的使用量降低到只有浮点解决方案的20%。

在FPGA架构中,查表也大幅节省约90%,因定点方案无需额外的查表来建构浮点运算。

若一个设计有10个FIR滤波器,其预期的功耗会随设计而扩展。表4显示在10个FIR滤波器设计的单精度和定点运行方案中,XCVU9P FPGA资源使用率的结果。此设计中,比较单精度浮点与定点运行的资源使用率时,有明显地差异。

表4:拥有10个FIR滤波器的两种资料类型解决方案的资源使用

? |

DSP48E2 |

查表(LUT) |

资源总量 |

元件使用 |

资源总量 |

元件使用率 |

单精度浮点 |

4,230 |

62% |

231,060 |

20% |

定点 |

850 |

12% |

19,730 |

2% |

显著的资源节省能获得多种优势,为设计人员带来深远的影响,有助于改善设计的功能集、功耗、效能及成本。

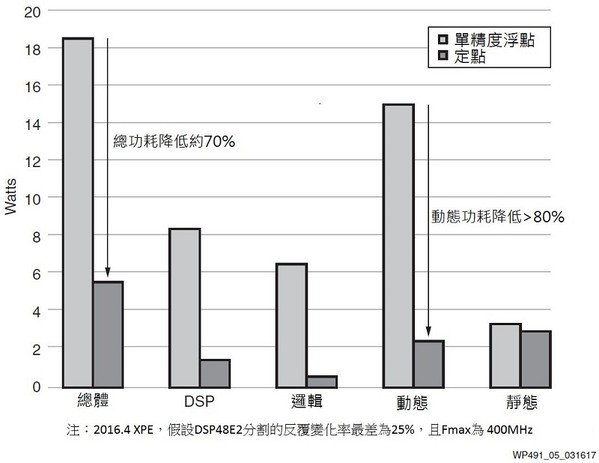

达到显著的功耗节省

节省大量的资源能够相应地降低功耗。

比较本文中提到单个FIR滤波器的两种运行方案,其功耗估算结果发现,定点FIR的功耗减少1.4W。两种方案中,元件的静态功耗略高于3W,而单个单精度浮点FIR设计的总功耗为4.7W。当定点FIR功耗为3.3W时,表示该设计的动态功耗节省80%以上。

再来看10个FIR滤波器的设计,可利用赛灵思功耗评估器(XPE)针对两种运行方案的功耗进行评估,并于表4中显示运算的资源,而图5为功耗节约的比较图。

| 图5 : 10个FIR滤波器实例:利用定点达到显着的功耗节约 |

|

在此10个FIR滤波器实例中,当把设计转换成定点资料类型时,其总功耗能节省高达70%。对于大量使用大量FPGA资源的浮点讯号处理设计,可透过将部分或全部浮点讯号处理链转换为定点,来实现巨大的节能效果。

削减材料成本

将浮点设计转换成定点方案,能大幅减少FPGA资源使用率。 FPGA资源的削减能降低材料成本。可通过以下三种方法来实现:

1.可利用最新的FPGA资源来扩增应用功能集。

2.由于FPGA资源大量减少及通过资料路径提高FMAX,因此FPGA的总体运算能力明显增加。

3.由于所需的FPGA资源减少,因此设计可迁移到更小型的赛灵思FPGA中。

相近的精度

通过比较单个FIR滤波器设计的两种运行方案之输出,会发现定点运行方案提供相近的滤波器精度,精度损失仅为 -100dBm至 -160dBm之间,并且能获得降低功耗与成本的优势。

然而,定点方案无法获得相同的动态范围,导致设计中出现可预测的精度损失。由于许多设计仅需低标准的精度,因此这并不构成任何问题,且这类设计与单个FIR实例类似,所以很适合转换为定点。

对于需要更高精度值的设计,有时可将讯号处理链中的中间值从浮点转换为定点,但此方案仅可让设计人员能够将特定部分(而非全部)转换为定点。最终,设计人员能够在需要时保持动态范围,并确保维持资料路径的精度下,同时充分发挥定点运行方案带来的部分优势。

改善延迟

在单个FIR设计实例中,可通过滤波器降低延迟,从浮点设计的91个时脉周期降低为定点运行方案的12个时脉周期。随着资源用量减少,尤其是DSP48E2分割的用量减少,则有望降低延迟。

除了降低延迟,在单个FIR实例中,还能提升FMAX;运行之后的FMAX可提升16%。

结论

赛灵思All Programmable元件和工具支援多种资料类型,包括浮点和定点的多种精度。使用浮点的设计与使用定点的同一设计相比,资源用量和功耗都来的更高,无论采用FPGA或其他如GPU的架构皆是如此。

某些应用领域已开始放弃浮点资料类型,例如深度学习推论工作负载运用INT8或尽可能地使用更低的精度,这已经成为明显的产业趋势。

如今的设计环境极具挑战,散热及功耗的要求越来越难以满足,因此设计人员必须评估各种方法来降低功耗,其中一种选择就是将浮点设计转为定点。

若使用C/C++,Vivado HLS等赛灵思工具有助于简化转换过程。

设计人员必须对定点资料类型的转换进行充分权衡,并充分理解这样做所能带来的巨大优势。

继续使用浮点虽是通向市场的捷径,但其成本较高。因此,若投入时间与精力转换成定点,将能降低资源使用量、成本和功耗,且降低效能损失,进而获得更大的优势。

(本文作者Ambrose Finnerty1、Herve Ratigner2为Xilinx公司1DSP技术行销主任工程师、2软体应用工程师)

笔记:

1.DSP系统产生器原本不支援FP16,但支援客制化FP16。

2.浮点运算核心支援转换→定点到浮点、浮点到定点转换,以及浮点到浮点的精度变换。