芯片制造技术在发展过程中每一个技术节点上都面临着极大的挑战。以前,摩尔定律预言业界对需求有稳步增长,总是会有买家购买密度越来越高的FPGA,因此,可以逐步克服这些挑战。军事设计人员根据设计任务中数字逻辑性能(以及价格敏感程度)的关键程度,而采用高密度逻辑组件以减小体积、重量和功率消耗,他们既是设计的「早期用户」又是「追随者」,在整个设计周期中都可以发现他们的身影。

随着芯片制造技术向尺寸更小的新制程技术节点迈进,制造商和数字设计人员都需要做出有一定风险的决定。厂商要保证在合适的时间以合适的价格启动下一个制程节点,而设计人员需要的是功能和性能的提高,能够抵消复杂的设计技术和芯片交付进度所带来的风险。这些要求促使Altera加速开发40-nm 芯片,在2009 年年初为军事用户提供密度更高、速度更快的收发器技术。军事用户可以放心的是,在制造设计和产品上已经采用了标准风险管理技术。由于在40-nm FPGA 的风险和机会问题上与军事客户及时沟通,Altera 帮助数字设计人员有效的衡量如何在国防电子领域采用大容量与高功率效益组件。

军事用户需求

FPGA 军事用户有各种各样的设计需求,但主要集中在其当前设计FPGA 的特性上(参见图一)。密度极高的FPGA 主要应用领域是雷达和电子战,以及保密通讯中的大容量波形处理。这类系统越来越多的采用了数字升频和降频、采样、快速傅立叶变换(FFT)、脉冲压缩和滤波功能,单芯片系统(SoC)解决方案支持分辨率更高的多个传感器信道,从而提高了现有传感器的辨别能力。

位于系统核心的FPGA

目前,Altera公司Stratix IV 系列中的FPGA晶体管密度(可用晶体管)和处理器以及DRAM 处于同一水平上。图二所示为处理器、内存和可编程逻辑晶体管密度的增长曲线。

随着这些复杂组件的出现,可以透过FPGA 设计实现算法更复杂、组件数量更少、更灵活的系统。这种灵活性源自大量的设计投入和验证。

产品历史

今天的军事应用主要使用130-nm、90-nm 和65-nm 制程技术节点制造的FPGA。Altera等厂商每一代FPGA产品除了符合摩尔定律的发展,而且还帮助军事用户在功率消耗管理、专用数字讯号处理(DSP)逻辑和嵌入式内存等方面发挥了优势。嵌入式软式核心处理器和整合微处理器为设计人员在组件整合上提供了更多、更灵活的选择。

而Altera和竞争对手在每一个芯片开发节点发布FPGA 产品时的主要竞争表现,在于率先实现高密度逻辑的投产上,然后是推出具有高速序列收发器的FPGA 型号组件。然而,这种产品发布齐头并进的形势在65-nm和40-nm制程节点上发生了战略性转移,Stratix IV GX FPGA 是最先具有收发器功能的组件。

过渡到40 nm的机遇

台积电(TSMC)为Altera提供的65 nm FPGA 测试芯片在设计和制程技术上获得了相当的成功。逻辑模块和收发器设计都成功通过了测试,可以放心进行生产,促使该公司充满信心地从65-nm架构过渡到40 nm。早期40-nm 制程技术的Stratix IV 测试芯片同样获得了成功。

Altera和台积电并没有满足于65-nm 产品的成功,而是看到了加速过渡到40-nm组件的机会,将工程资源集中在尽早为军事客户提供40-nm 收发器组件上。由此,进一步推进军用设计,在收发器技术节点上增强风险管理。表一列出了Stratix IV 40-nm组件在国防系统中的优势。

(表一) Altera Stratix IV 40-nm FPGA 组件的技术优势

改进 |

优势 |

高速680K逻辑单元 |

在一个芯片中,整合更多的功能到更大的设计之中 |

灵活的功率消耗设置 |

控制性能和功率消耗达到平衡 |

高达1360个18 x 18乘法器 |

密度更高的讯号处理 |

高达22.4Mbits内存 |

使用更少的芯片外资源 |

高达48个收发器,速率高达8.5Gbps |

大大提高了芯片内 / 外带宽 |

高达16个全局时钟,88个本地时钟 |

更灵活的时钟管理 |

过渡到40 nm 的风险

过渡到新技术节点有机会和优势,但是也要综合考虑所遇到的风险。军用系统FPGA 设计人员可能遇到的风险包括大容量Stratix IV 组件的及时交付(最初交付和全面量产)、新组件的制造缺陷、价格不确定性,以及设计复杂度和组件利用率等。还需要重点考虑的是在以前技术节点所设计的专用硅智财(IP)的使用(或者优化)问题。只有对这些风险进行研究和管理才能充满信心地采用40-nm Stratix IV 组件进行设计。

机会和风险管理

40-nm制造技术利用了65-nm架构的所有优点,二者在同一平台上进行开发。这不但降低了方法上的风险,生产风险、设计复杂度和编译时间、跨平台设计导出等方面的风险都得到了有效控制。

生产

系统设计人员为什么要关心FPGA的生产方法呢?军用电子用户可能是对深入了解可编程逻辑供货商最感兴趣的,原因是多方面的。军用电子系统具有较长的设计和验证周期。军用设计规划人员必须认真考虑是应该采用落后于竞争对手,但是经过市场检验的芯片技术,还是过渡到尖端技术,以提高组件速度和带宽。衡量尖端技术风险最有效的方法是评估FPGA 生产技术的主动风险管理程序。

FPGA 供货商进行决定时考虑的一个重要因素是现有的生产关系。风险因素包括制造商关系是否牢固,有多少年的合作关系,制造商的技术领先地位等。任何芯片技术节点的生产风险都可以表示为供货商进度风险和组件可靠性风险。Altera 与台积电的生产合作关系超过15 年,在40-nm 上共同进行研究和开发。这一投入的回报是Altera 成为40-nm组件的首批客户。

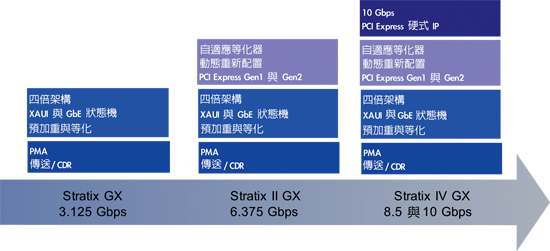

在生产上的另一风险因素是收发器设计的连续性问题。采用了一致性较好的方法以及拥有稳固的设计团队,收发器设计能够以最小的风险从一个芯片节点移植到下一节点。如图三所示,Altera 在每一代Stratix收发器技术上都保持了相同的收发器设计团队。

| 《图三 Altera收发器依靠同一个设计团队,建立在一致的制程技术上。》 |

|

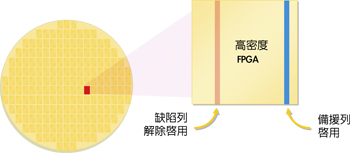

Altera 在生产上采用了专利备援技术(图 4),保证Altera 及其客户能够提高产量,降低生产风险。该技术使Altera 充满信心地采用最新制程技术,而且降低了移植风险。该技术支持每一个逻辑行在早期制造测试中分别启用和解除启用,从而显著提高了芯片可用率。

| 《图四 Altera专利备源技术降低了量产的风险》 |

|

设计复杂度和编译时间

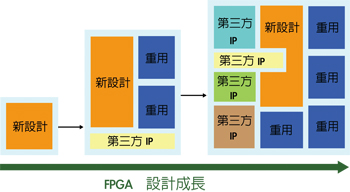

设计大容量FPGA时的部分风险包括设计复杂度和编译时间对国防电子设计进度的影响。如果不采用灵活的方法来管理设计软件,设计时间会急剧增长,如图五所示。为控制风险,Altera 在设计工具上进行了大量投入,为大容量Stratix IV FPGA 推出了新一代工具。

| 《图五 随着FPGA规模的提高,设计复杂度既是风险又是机会》 |

|

FPGA 设计中的编译时间与设计工具环境、设计复杂度和约束环境有关。用户对功率消耗和芯片的约束越多,布局布线的时间就越长。Altera 的QuartusR II 设计软件透过平行处理、宽总线操作系统,以及用户工具(渐进式编译和逻辑锁定)支持,实现了设计划分和分区锁定,从而降低了FPGA 布局布线的编译时间风险。

实现跨平台FPGA设计

随着FPGA复杂度的不断提高,很少有设计是从头开始逐步完成的。重新使用IP模块是军用FPGA设计的关键,可以从第三方购买这些模块,也可以在工程组织中对其进行包封,重新使用。

购买或者重新使用高速序列数据内部核心是实现系统设计的低风险方法,特别是这些内部核心得到商用性能标准认证的情况。然而,对于算法模块和非常专业的IP,人们对使用第三方应用程序心存疑虑。在这种情况下,相对于降低开发风险,人们更关心通用性和性能风险。

在国防项目中实现小型「模块」IP 时,有四种特殊的风险。第一是使用相似的FPGA 设计工具和组件,将IP模块从一个设计移植到另一设计。虽然不用从头开始建立每个建构模块,从而降低成本,但是存在着IP模块不能正确包封的风险。这意味着重新使用模块时,可能要满足不需要的时序约束。解决这一问题最好的方法是提供详细的内部IP文件档和第三方合成工具。

第二是在不同代FPGA之间移植IP模块的风险(例如,从90 nm 或者65 nm 向40 nm 移植)。对于FPGA供货商提供的IP,在所有尺寸上重新发布这些IP模块,以提高性能。但是,IP 移植到更现代的组件中时,其性能和时序会受到影响。几乎所有FPGA 供货商都提供设计分区工具,评估对IP的影响,对模块进行改进。

在需要实现大批量、成本敏感、抗辐射能力较差的应用时,面临的第三种风险是把IP从FPGA移植到ASIC的问题。大部分关于FPGA至ASIC设计的建议是采用认证过的第三方IP。而对于HardCopyR ASIC设计,IP移植几乎没有风险。FPGA和ASIC的设计软件相同,从同一个HDL设计中产生FPGA和ASIC网表,甚至电压变化都相同。

最后也是最大的风险是IP在不同FPGA供货商之间移植的问题。几家公司开发了「FPGA 未知」应用层来嵌入运算产品,该项目得到政府客户的支持,他们希望在国防产品中采用两家供货商这种模式。在国防电子领域,「中途换马」的风险非常大,但是采用Quartus II等单流程软件设计系统能够大大降低这种风险。

结论

最后也是最大的风险是IP在不同FPGA供货商之间移植的问题。几家公司开发了「FPGA 未知」应用层来嵌入运算产品,该项目得到政府客户的支持,他们希望在国防产品中采用两家供货商这种模式。在国防电子领域,「中途换马」的风险非常大,但是采用Quartus II等单流程软件设计系统能够大大降低这种风险。

如表二所列,对40-nm FPGA 技术机会和风险的评估主要集中在产品及时面市、设计效能和数字讯号处理换代上。可以根据国防客户特殊的项目需求和进度安排进行更深入的风险分析。

(表二) 40-nm FPGA 设计的风险和机会 |

风险 |

|

影响:技术问题,延迟

|

- 芯片内和芯片外带宽的尖端技术

- 高密度组件上最高的逻辑、乘法器、内存和电源效率

- 能够移植到具有收发器的结构化ASIC

影响:大大提高了每一代数字逻辑的性能

|

风险管理 |

机会管理 |

- 多系列测试芯片,优异的结果

- 重新使用高功率效益的65-nm制程,对特性充满信心

影响:在交付40-nm技术上充满信心

|

- 在高密度设计效能上加大投入

- 与业界芯片制造领先者独特的合作关系

影响:在40-nm技术上,可马上进行设计和实施的机会

|

对于大部分新技术,采用全功能Stratix IV FPGA 需要对很多应用的架构进行改进。采用可编程逻辑或者可重新配置软式核心处理器,能够有效地实现军用嵌入式系统的管理和处理功能。采用Stratix IV 进行设计,借助大量的逻辑资源,更多的IP 透过简洁的VHDL 程序代码实现,军用系统开发人员在设计过程和资源重新使用上将得到相当大的回报。

(本文作者任职于Altera军事和航空航天事业部技术市场经理)