先進的CMOS製程技術使IC設計人員能夠提供更高性能的元件,但也增加了額外電路板級靜電放電(ESD)保護以確保終端產品可靠性的需求。

IC製程技術趨勢

先進的CMOS技術使半導體供應商能夠生產特徵尺寸日趨減小的積體電路(IC)。減小IC特徵尺寸的優勢不計其數。特徵尺寸越小,就使電路可以佔用更小的面積,使IC能夠以更小的矽片面積承載更多功能,而且每顆IC的成本更低。

特徵尺寸更小的CMOS電晶體的性能也更高。結果就是功能更多、性能更高、成本更低的「三贏」局面。CMOS製程尺寸已經大幅縮小;成熟的0.18μm或0.13μm製程可為訂製類比/混合訊號專用積體電路(ASIC)項目提供高性價比的選擇,與此同時,領先的數位IC設計已經瞄準諸如45nm、32nm甚至是28nm等幾何尺寸。

更小幾何尺寸的副作用是要求更低工作電壓。如果不能降低IC工作電壓,將可能導致門氧化物失效及電晶體老化等其它可靠性問題。更低的電壓同時帶來正負兩方面的影響。正面影響是更低的電壓導致功率耗散更低,這也是當今流行電池供電手持電子設備所注重的一項主要優勢。

負面影響是帶來諸多電子設計挑戰,如減小動態範圍,以及伴隨供電電壓降低而來的訊號雜訊比(SNR)降低。此外,從電腦到手機等電子裝置易於遭受的靜電放電(ESD)等電氣應力並未隨著IC技術進步而改變電壓或電流的數量級。結果就是較低電壓的ESD事件可能損壞先進的IC。這就預示了應當如何設計電子系統來承受ESD。

為了理解這些,就有必要理解電路設計中如何納入ESD保護。IC級和系統級的ESD設計準則類似,因此我們將先探討IC級的ESD保護,然後擴充討論至系統級。我們然後就來瞭解電路板級ESD保護及恰當的電路板設計怎樣在系統級ESD設計中發揮重要作用。

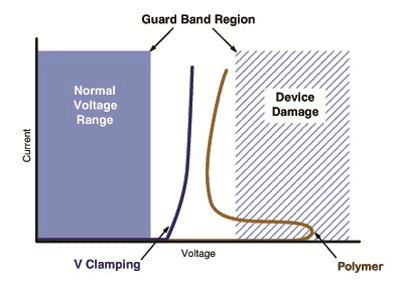

所有電子元件及電路都有預期的工作電壓範圍及安全防護帶,如圖1所示。超出此防護帶的電壓將引發電路損壞。由於先進的製程技術要求更低的工作電壓,安全防護帶也變得更窄。ESD保護元件用於在遭受ESD應力期間將電壓維持在安全防護區域內。

隨著安全防護區域縮減,就需要導通阻抗更低的ESD保護元件,從而使電壓維持在安全防護區域內。過壓保護的典型實現途徑是使用通過提供低阻抗路徑將電壓鉗位至安全防護帶區域內的元件,如圖1中的電壓鉗位所示。

| 圖一 : Operating-voltage regions for ICs and ESD-protection devices |

|

圖2所示的是I/O接腳片上ESD設計的例子。

在圖2左側,電壓鉗位元件置於輸入接腳,用於在電壓超過正常工作電壓範圍時導通及提供通往IC接地匯流排的低阻抗路徑。這就保護敏感的接收器免受電壓及電流過大的影響。

這些鉗位元件可以是單顆齊納二極體、如圖所示的背向齊納二極體,或是特別設計的由nMOS電晶體構成的驟回(snapback)結構。

第二種流行方法是使用控制二極體(steering diodes)及電源鉗位,如圖2右側所示。I/O對地的負向應力將通過控制二極體傳遞至地,防止應力施加在輸入門上。對地的正向應力將通過控制二極體傳遞至VDD及電源軌。

在VDD與地(GND)之間的電源鉗位元件將把電流應力從VDD匯流排傳遞至地。電源鉗位元件可以是簡單的齊納二極體或是有源電路,此電路檢測VDD與GND之間的意外電壓,並導通VDD與GND之間的大電晶體,提供低阻抗路徑。在I/O與VDD之間遭受應力的情況下,此電路的工作特性類似。

圖中右側中的兩組控制二極體及電阻是初級及次級保護策略的一部分。提供初級保護的最接近I/O接腳的一組二極體,旨在承載大部分應力電流。提供次級保護的是最接近敏感MOS電晶體門的一組二極體。某些應力電流將流經次級保護電路,但電路不僅對流入次級保護電流的電流進行限流,電阻上的壓降也將幫助啟動初級保護。在探討系統級保護時還會注意到這種策略。

IC安全操作ESD設計與系統ESD設計之間的主要區別在於應力的大小。構建在大多數IC內的ESD保護旨在確保IC在ESD受控的生產廠(ESD事件鮮有發生,而且強度低)中能以高良率得到處理。如今,針對先進IC的ESD保護目標是1000V人體模型(HBM)及250V充電元件模型(CDM)。1000V HBM的峰值電流約為0.67A,相應的衰退時間為150ns;CDM電流可達數安培,但持續時間可能僅為數奈秒(ns)。

這可以與測試系統在ESD事件下強固性的IEC61000-4-2標準規定的8kV應力條件下30A峰值電流、特徵時間約為50ns進行對照。顯而易見的是,如果沒有特別的設計考慮,先進IC的輸入及輸出(I/O)接腳在系統級ESD脈衝條件下無法存續。

如果IC安全操作ESD測試及設計與系統級ESD測試及設計之間的區別主要是數量級問題,何不在實際連接至USB、乙太網、HDMI及Display Port等系統級I/O的I/O接腳中設計系統級ESD強固性?在某些情況下,這是有可能的,但通常並不明智。ESD保護結構無法擴展到較小的區域,因為較小幾何尺寸IC中能夠用於ESD保護的空間有限。

系統級ESD電流大,不會擴展到較新世代的技術。以最先進技術設計系統級ESD結構需要的矽片面積大體上與以更成熟技術設計相同。採用更新技術的矽片面積的成本要高得多,因此,隨著技術變得更加先進,系統級ESD保護的成本也隨之升高。

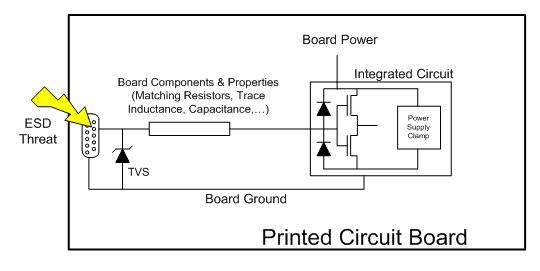

此外,對於高速資料線路而言,有必要在保護設計中維持極低電容。對於通常擁有極高矽摻雜等級並導致大電容的大多數先進技術而言,這可能極為困難。因此,使用置於電路板上的ESD保護,如圖3所示的暫態電壓抑制器(TVS)元件,就變得極為可取了。

| 圖三 : 置於印製電路板(PCB)的板載ESD保護示例 |

|

ESD保護元件

系統設計人員可以根據應用及預計會出現的過大應力類型,從多種保護產品中進行選擇。

一種保護產品示例就是金屬氧化物壓敏電阻(MOV)。MOV對暫態事件快速反應,但它們的大電容在訊號線路上施加了大量額外負載。晶閘管浪湧保護元件(TSPD)通常用於電信及乙太網設備保護,使其免受大電流承載能力導致的浪湧影響,但他們的反應速度通常太慢,而且其導通電壓對於有效地ESD保護而言也太高。

TVS二極體

圖3所示的是使用TVS產品。TVS置於鄰近I/O連接器的地方。在理想的狀態下,TVS元件將先於IC的內部電路導通,並檢測完整的對地浪湧電流。實際上,通常TVS產品與IC內部構建的ESD保護結構會共同承載電流。這種配置極類似於前文探討的片上ESD保護的初級及次級保護(如圖2所示)。

置於電路板上的TVS產品相較於片上ESD保護具有優勢,因為走線電感及匹配電阻等電路板相關元件能用作ESD保護策略的組成部分,限制ESD電流流入IC,並提供幫助導通初級板載ESD保護元件的額外電壓降。安森美半導體生產寬廣陣容TVS產品,用於多種應用,而且設計提供業界領先的低鉗位電壓。

TVS二極體產品相較於MOV及聚合物ESD保護產品擁有優勢。MOV及聚合物對於正向及負向應力擁有對稱特性。TVS元件可以設計為提供對稱及不對稱特性。單齊納二極體擁有不對稱特性,以某種極性作為正向偏置二極體導電,並相反極性用作齊納擊穿二極體。這非常適合用於保護只包含單極性(如0至3.3V)的電路節點。背向二極體提供對稱回應,以正向及齊納擊穿導電的串聯組合導電,同時用於正極性及負極性。這非常適合用於保護相對於0V的對稱(如-3.3 V至+3.3 V)電路節點。

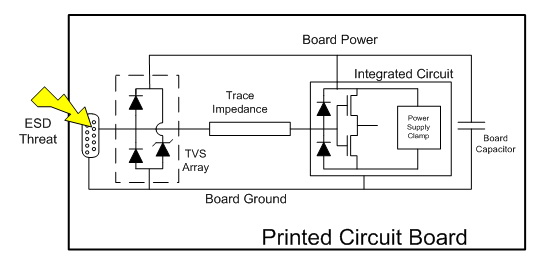

使用電源解耦

ESD保護陣列可以在保護策略中整合電源解耦電容。在ESD頻率,電源與地電平之間的μF範圍解耦電容提供了低阻抗的對地通道。TVS陣列中的控制二極體可將ESD電流引導進入電路板上的電源及地電平線路,大幅減小電路板上的電壓暫態,如圖4所示。

TVS陣列中的齊納二極體進一步限制電壓暫態。構建地陣列封裝中的齊納二極體也有極低電感,因此在消除ESD事件期間可能出現的電感型電壓尖峰方面極為有效。為了發揮效用,電路板級電容需要鄰近TVS陣列,且TVS陣列及電容的位置佈設都需要避免高阻抗連接,如既長又窄的走線。安森美半導體生產適合眾多應用的TVS陣列產品。許多產品針對特定應用,且其設計旨在簡化電路板佈局。

| 圖四 : TVS陣列及解耦電容用作ESD保護策略組成部分的示例 |

|

保護高速資料線路

當TVS二極體用於保護高速資料線路時,TVS二極體的電容將導致訊號干擾,導致資料完整性降低。圖5及圖6所示的眼圖比較了未採用保護及採用了65pF電容TVS二極體的USB 2.0訊號線路,展示了電容性負載如何使訊號轉換失真。圖6中穿過USB 2.0範本(mask)的跡線彰顯了增加電容性負載時令人不可接受的訊號完整性。設計人員必須鑒別出能夠保護敏感線路而不會增加降低訊號品質之電容的ESD保護方案。

| 圖六 : 採用了65pF ESD保護二極體的USB 2.0資料線路眼圖 |

|