系统-技术偕同最佳化(system-technology co-optimization,STCO)—透过3D整合技术支援—被视为延续微缩技术发展之路的下一个「开关」。爱美科研究员暨3D系统整合计画主持人Eric Beyne,以及爱美科3D异质整合计画主持人Julien Ryckaert,将在本文说明STCO原理、展示3D技术工具箱,并提出两件具前瞻性的案例:逻辑对记忆体的异质整合(logic on memory)和晶背电源供应(backside power delivery)。

随DTCO而来的STCO…

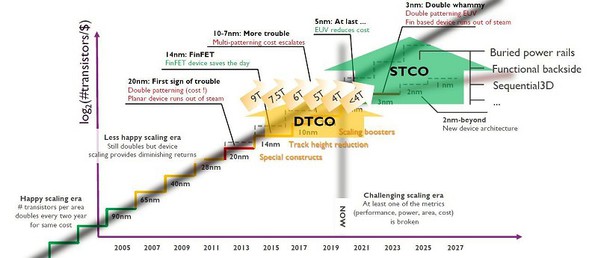

半导体产业活在由摩尔定律驱动的「快乐微缩」时代好几年了。在这个时代,单就尺寸微缩技术(dimensional scaling),就能带给每个新技术世代在功耗、性能、面积和成本方面所需的好处。然而,半导体产业在过去15年间,已不再沿着这条微缩技术的康庄大道。尺寸微缩技术的收益开始递减,划下这个时代的句点。

自10奈米的技术世代之后,传统的微缩技术开始因设计-技术偕同最佳化(design-technology co-optimization,DTCO)而完善,集结来自技术和设计领域的专家。在DTCO的时代,缩减轨道高度和发展更多加速结构微缩技术(structural scaling booster)的作法被采用,标准元件和静态随机存取记忆体(static random access memories,SRAM)因而得以微缩至极紧密的程度。举例来说,加速微缩技术包括自对准闸极触点(self-aligned gate contact)、金属闸极截止(metal-gate cut)和超导孔(supervia)。

但随着我们更进一步发展,并回顾DTCO能在系统单晶片(system-on-chip,SoC)层面带来的好处,可以想见这些好处会达到某种饱和—尤其是当我们开始注意到系统单晶片的全域存取(global access)和电源供应技术。

因此,以3奈米技术和后续技术节点来说,我们需把微缩技术的重心从逻辑元件层次转移到系统层次。所以,DTCO正在朝STCO导向的方法进化。

| 图一 : 从设计—技术偕同最佳化(DTCO)到系统—技术偕同最佳化(STCO) |

|

STCO:去整合的妙方

一般来说,STCO包含系统单晶片的去整合(disintegration)和再整合(reintegration)。系统单晶片由各种(异质的)子系统(功能元件)组成,这些子系统由复杂的布线图相互连接。在将系统单晶片去整合的时候,应该巧妙地决定要在内连导线阶级中的哪一层分割(partition)系统。

但可以用什么方法做出这个决定呢?哪些元件归属同类?又哪些元件应该分别处理?我们通常必须在导线粒度和技术异质性间取舍,前者指的是系统中的不同零件将以何种粒度重新相连。比方,如果我们想达到非常精密的粒度,就不能重新连接多种不同技术。

去整合之后,这些个别的子系统就能以最合适的技术分别进行设计和处理。

照着去整合和再整合的方法,我们将不再遵照以往一直被用来制作更高阶系统单晶片的指导原则:互补式金属氧化物半导体(complementary metal-oxide-semiconductor,CMOS)的广用性。

目前为止,晶片上所有的不同功能元件(例如包括:逻辑元件、记忆体、I/O介面、电源元件等)都被连接在同一个CMOS技术平台。对这项CMOS技术进行微缩,目前已发展出性能更高的系统。

但随着系统单晶片变得越来越异质,采用另一个不同的处理技术会更有利(这项技术也可以是某个技术的多节点变化),以因应子系统的不同需求。比如说,记忆体的处理不需和逻辑元件相容。或者,想想看感应器和其他类比功能元件,运用终极微缩技术其实对这些元件来说没什么帮助。就这些功能元件来说,可以采用更简易的处理过程和间距较宽松的微影技术(lithography)。

透过这个方法,我们预期能够在功率、性能、面积和成本方面获得更多进展—为将来的电子系统提供微缩的新契机。

再整合:3D整合技术登场解救现况

在去整合系统单晶片和优化不同子系统后,这些子系统需要透过现有的一种3D整合技术,巧妙地再次进行整合。

不同的3D整合技术可应用在内连导线阶级中的不同层,囊括具指数级差异的内连导线密度(也就是每平方毫米的连接数)—从毫米级到奈米级。

这项3D内连导线的技术全貌可以下方图表说明。此图表描述了有关可实现之3D内连导线密度和间距的各种3D整合方法。

在图表显示晶片结构较粗糙的左方,是系统子元件间仅需少数连结时一般会采用的技术。目前零组件的分割是在封装的阶段,透过将封装(package)相互堆叠完成。动态随机存取记忆体(dynamic random-access memory,DRAM)的堆叠已展示了这种系统级封装方法(system-in-a package,SiP),粗接点间距可小至约莫400μm。多晶粒(multiple die)作为一种代替系统级封装的方法,能在单一封装中运用被动中介层(passive interposer)来进行整合—又称2.5D整合。举例而言,2.5D整合现在正被用来生产「小晶片(chiplet)」型的产品。

或者,扇出型晶圆级封装产品数量众多(对诸如智慧型手机的行动应用来说,这是颇受欢迎的解决方案),2.5D整合可以应用在这些产品的其中之一,因为具2.5D整合特色的产品可能得以实现在小配置规格中低成本、宽I/O的晶粒到晶粒互连(die-to-die interconnect)。很多这种技术运用水平和垂直式的内部互连。

3D内连导线的高密度可透过晶粒到晶圆的堆叠技术实现,晶粒成品被黏在经过完全处理的晶圆上。晶粒间以矽穿孔技术(through-Si vias,TSVs)或微凸块(microbumps)相连。爱美科的目标是将这些微凸块间的间距缩短至10μm以下。

接下来是实现真正的3D系统单晶片的晶圆接合技术(wafer-to-wafer bonding)。这种系统单晶片是各种功能元件和技术分区进行异质堆叠而成的封装,其内连导线间距大约是1μm。有两种技术可供应用:异质晶圆接合技术(hybrid wafer-to-wafer bonding)或介电层晶圆接合技术(dielectric wafer-to-wafer bonding)。

目前最高的内连导线密度是透过循序的处理过程达成。电晶体最终能进行相互堆叠,接触间距(contact pitch)小至100nm。每当晶片上层需和底层进行微影精度对准时,循序处理的真正用处便浮现。 「电路下阵列技术(array under CMOS)」,是一种可能受惠于循序处理的有趣应用—它需将周围电路和阵列分离。循序处理也可应用在感光元件(imager)和记忆体选择器(selector for memory)等元件上。

非比寻常的发展蓝图

值得注意的是,我们不该将这张3D技术全貌解读为由左而右排序的时间表。没有一个封装技术能满足所有需求。

反的,不同3D整合技术相互并存,甚至能在同一系统中共存。

此外,随着内连导线密度和间距及时改善,每种技术都有各自的发展蓝图。但要决定出哪个是最佳3D整合技术,完全由应用本身和分割后各部件间的「流量」决定。这个最佳技术由多项技术合成,让单一系统得以整合在更小的配置规格中,且性能、功耗优化,生产成本更低,以支援STCO。

当逻辑元件和3D技术连结:两件STCO案例

系统单晶片的各种功能元件(像是感光元件或记忆体元件),藉由现有的3D整合技术之一,已应用了分割和再整合技术。然而,截至今日,逻辑元件仍多是被置于「3D设计图」之外。下述两件案例说明此议题在近期的改变:逻辑对记忆体异质整合以及晶背电源供电系统的案例。

这两件案例将说明逻辑元件和3D技术如何在STCO架构中连结,以及设计良好的分隔技术能以什么方式为未来CMOS微缩技术提供转机。

这两件案例中,我们探讨系统单晶片的三个关键功能元件:逻辑核心、快取记忆体与储存器、电源供应元件。

逻辑对记忆体的异质整合

在传统的系统中,记忆体阵列置于其支援的逻辑核心旁。这样的配置使得内连导线长度居于适中,这个长度由两元件间的间隙和单一晶粒上的凸块间隙决定。

或者,系统可以应用功能元件分割和晶圆接合技术,把记忆体垂直堆叠在逻辑元件上方。记忆体可透过记忆体优化的处理程序,在单一晶圆上制造,而逻辑核心可在另一片晶圆上制造。

这么做的好处包括潜在地缩减晶粒面积,并且明显地缩减元件的实际尺寸(footprint)。而且还能让功能元件(如:L2快取)置于距离其支援的逻辑元件更近的位置,平均的内连导线长度便是两元件间的垂直间隙。这使性能(内连导线频宽)得到提升,而功率耗损降低。

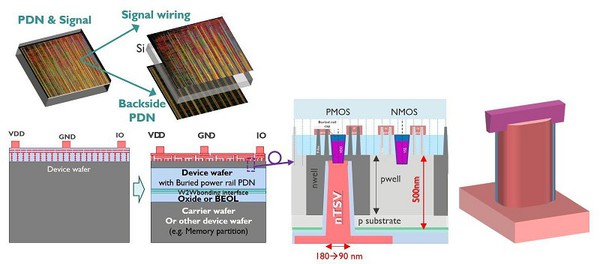

晶背电源供应

电源供应网路(power delivery network)的目标便是提供元件电力和参考电压给晶粒上的主动元件。这个网路其实就是内连导线的网路,和讯号网路(signal network)截然不同。一直以来,讯号系统和电源供应系统的处理都在半导体的后段制程,也就是位于矽晶圆的前侧。

我们也可以想像从晶圆背面提供全域功率(global power)。从晶背那里,内连导线的网路可和埋入式电轨(buried power rail)连接,这些电轨属于一种加速微缩技术,以区域电轨的形式在晶片的前端制程中埋入晶片。

| 图三 : 功能元件的晶背电源供应网路原理是应用奈米级矽穿孔技术,以穿过超薄的矽元件层,接触埋入式电轨。 |

|

应用上,可以透过先将CMOS晶圆以晶圆接合技术连接在载体上,以进行晶背处理。接着,晶背以极高的薄化程度加工(薄化至大约数百奈米)。如此,从晶圆正面流通至晶背的奈米级矽穿孔得以曝光,并以极精密的粒度相连。

藉由直接从晶背传输电力至标准元件,爱美科团队在近期用实例证明了此技术可带来减少30%面积的微缩好处。除此之外,在晶背布建电源供应网路可以让晶片的正面免于布建电源网路绕线,能够降低后段制程的复杂度。还能改善电源电压下降的问题(或称压降,是在后段制程中电阻增加所致),最多能提升15%性能。

有趣的是,这种功能元件晶背处理的概念可以延伸应用至电源供应以外的地方。

我们可能开始想着要在晶背布建其他功能元件,举例包含:金属-绝缘体-金属电容(metal-insulator-metal capacitor,MIM capacitor)、静电保护元件(electrostatic discharge devices,ESD devices)或氧化铟镓锌电晶体(indium-gallium-zinc-oxid transistor,IGZO transistor)。

结语

随着DTCO渐渐失去动能,我们正处在新世代的前夕:未来会是STCO的时代,逻辑元件层次的微缩将由全域系统层次的微缩补足。 STCO需将系统单晶片去整合,而后应用现有的3D整合技术之一将系统单晶片再整合。这些技术可应用在3D内连导线阶级的不同层,从封装到晶粒、到晶圆、到标准元件,甚至到电晶体。两件案例:晶粒上逻辑元件的异质整合、晶背电源供应,说明了这个STCO架构正如何影响逻辑元件领域,为接续微缩技术发展之路提供后续关卡的开关。

(本文由爱美科授权刊登;作者Julien Ryckaert为爱美科3D异质整合计画主持人、Eric Beyne为爱美科3D系统整合计画主持人;编译/吴雅婷)

*刊头图 (source: wallpapercave.com)