迎合现今AI热潮对於先进逻辑和记忆体需求,由比利时微电子研究中心(imec)协调整合的欧洲研究计画奈米晶片(NanoIC)试验制程,持续致力於加速2奈米以後的晶片技术创新。近日更宣布推出两套全新制程设计套件(PDK),包含用於先进逻辑微缩技术的14埃米(A14)路径探寻PDK,以及用於先进记忆体创新的嵌入式DRAM(eDRAM)系统探勘PDK。

|

| 目前由eDRAM PDK提供一套探索嵌入式记忆体解决方案的虚拟平台,可填补外接DRAM与内建SRAM之间的技术缺囗。 |

透过免费开放这类NanoIC试验制程的先进PDK在推进半导体创新方面发挥关键作用,连接早期阶段的研究探索与现实世界的整合。将有机会让设计人员在新兴技术的硬体问世之前,提早取得实际的设计规则和实作工作流程;并提供使用者和新创公司探索先进技术节点和嵌入式记忆体设计的独特管道,预测整合挑战和叁照实际的微缩指标,为设计进行基准测试。

作为首批推出的制程设计套件,A14路径探寻PDK提供用来探索14埃米节点的视觉设计环境,用於新兴微缩加速器的晶背金属接点。此有别於过去2奈米(N2)制程设计套件,运用中段制程矽穿孔封装(TSVM)的结构来支援晶背供电,14埃米节点进一步采用更紧凑的直接晶背接点方案来取代TSVM。

这套新架构直接从晶圆背面建立连接到闸极的电源布线,还不需要晶圆正面的复杂金属布线,成功在相同频率和单元密度下,达到比2奈米更低的IR压降、提供18%面积增益和减少7%功耗。该套件包含完整的162-SDC元件库,并获得两大电子设计自动化(EDA)厂商益华电脑(Cadence)、新思科技(Synopsys)的支持。

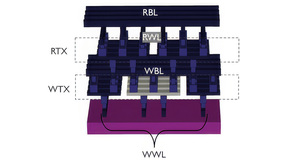

此外,为了有助於推动A14 PDK探寻逻辑路径,NanoIC试验制程也推出首款eDRAM系统探勘PDK,以提供具备高密度及低延迟的内建记忆体,拉近记忆体与处理单元的距离,也是在先进运算架构缩短延迟和改良功率效率的关键策略。

目前由eDRAM PDK提供一套探索嵌入式记忆体解决方案的虚拟平台,可填补高密度但高功耗的外接DRAM,与高速但尺寸受限的内建SRAM之间的技术缺囗。利用eDRAM PDK聚焦资料密集和AI运算的系统级表现,可让设计人员藉此评估用来缩短高密度记忆体与处理器、图形处理器(GPU)之间距离的新兴记忆体架构和整合策略,减少资料传输距离,改良能源效率,以及提升整体系统性能。

展??未来,eDRAM PDK将发展成一套完整的系统探勘平台。这一步发展将能让设计人员突破虚拟验证,并分析完整的系统级交互作用,更深入研究嵌入式记忆体这类用於AI与资料密集运算的关键元件。随着平台趋向成熟,未来的研发阶段包含硬体验证,还有最终在NanoIC试验制程进行原型设计和投片(tape out)的发展机会。