IC制程技术的持续发展,为电子商品的市场带来难以计数的新机会和成长动力。最近更协助系统厂商以消费者所能负担的价格,提供前所未有的效能及特色。矽晶片容量与消费者对电子产品使用需求的同步成长,则促使设计技术进一步发挥其潜能。

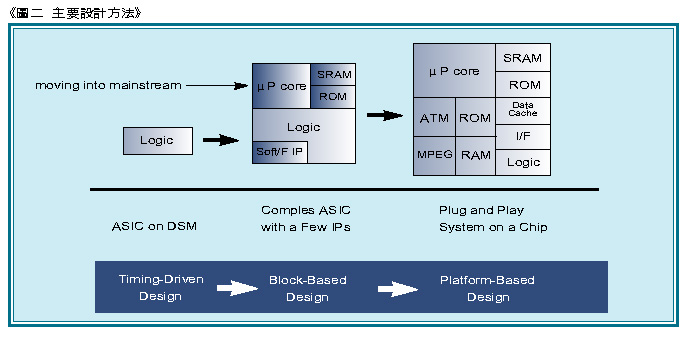

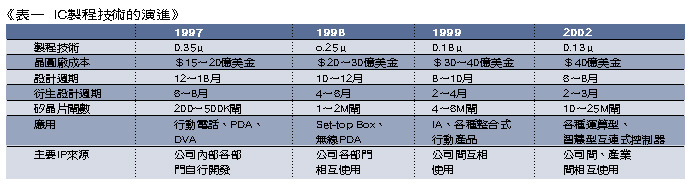

虽然IC制程技术持续加速推进,但如今设计再利用(Re-use)与设计自动化(Design Automation)技术却似乎成为开发系统单晶片(SoC)的主要技术障碍;同时这项障碍造成的生产力断层也在逐步加大之中。 (表一)所示为不断增加的复杂度、首次及后续设计周期的减少、设计再利用及应用整合等条件的组合等,均已对电子设计程序造成一个根本上,无可避免的不连续性。这些现象遇见了IC制造技术的水准,可望将复杂的系统完全整合在单一晶片上,但要达此理想,还需倚赖一套先进的设计流程,方能奏效。

现有的IC设计方法,仍不足以辅助最进步的制程,达到系统单晶片整合的目标。以1980年代早期晶元程式库(Cell Library)带动的ASIC作为典型的例子,现代的ASIC设计也必须提升至更高的设计生产力水准,才能满足各项功能要求。这种设计方法的演进不只可减少开发的时间与精力、增加可预测性、降低SoC设计的复杂度,更能减少制造过程中所涉及的风险。

这种转移到SoC设计的必然方向,有赖于两项产业的发展趋势:一是因应SoC元件及衍生产品快速设计之需要而促进以应用为主之IC整合平台;其次是可广泛取得的再利用虚拟元件。

何谓系统单晶片(SoC)设计?

首先我们必须将SoC设计定义成一个标准作业模式,并且可广为业界接受。 1996年成立的虚拟插槽联盟(Virtual Socket Interface,VSI),是以培养发展及确认IP再利用区块的设计与整合标准为理想的最具公信力组织。该联盟将系统单晶片定义为「高整合度的元件,也同时称为矽级晶片、单晶片系统、系统级LSI、系统级ASIC,或系统级整合元件。」Dataquest也曾定义SoC元件为具有「超过10万闸及至少有一个可编程核心,并内建记忆体的高整合度晶片。」

综合上述的理论,SoC设计大致可定义为一个极复杂的IC,它将一个终端产品的主要功能核心整合至单一晶片或晶片组之中。一般而言,SoC设计通常会纳入一个可编程处理器,内建晶片上的记忆体,及一个硬体加速单元。它同时也拥有介面电路与外界的元件或系统连系。 SoC设计同时包含硬体与软体模组,由于与真实世界直接连接,SoC设计也经常涉及类比元件,未来更有可能加入光电/微机电系统(Opti/MEMS)模组。

日本的电子产业协会(Electronic Industries AssoCiation)已针对公元2002年前设计Cyber-Giga-Chip,提出一套完整的电子设计自动化(EDA)技术发展蓝图。此一设计共包含DRAM、快闪记忆体(FLASH)、CPU核心、数位讯号处理器(DSP)核心、讯号处理及协定控制硬体、类比方块、特定用途硬体单元及晶片上汇流排等,充分说明了未来SoC设计所涵盖的复杂程度。

| 《图一 关键性技术的历史演进》 - BigPic:671x348 |

|

关键性技术

IC制程技术改变所造成的设计模式不连续性,需采用新的架构加以克服。关键性技术是用来转移到下一代设计方法的建构基石。一般而言,新的制造技术会与特殊的设计方式共同搭配使用,才能彰显优势。通常为了早日完成首件产品设计,往往会在研发过程中面对许多挑战。

因此在设计初期运用的各种特殊设计手法,经常会带来许多意想不到的效果。由于这些新技术为设计能力、功能性成本、设计方法及改变工程步骤,提供了显著的改善助益,因而自然成为刺激更大幅改变的必要手段。

回首设计技术的演进,我们可以很容易地认定许多重要的技术,如(图一)。例如,闸级模拟驱使设计验证容量增加到足以因应矽容量的规模;但在闸级逻辑范围内的设计,却意味着被迫接受模拟器及相关程式库模型建立准确度的限制,这将导致基本设计法则的根本改变。

类似的情形也发生于RTL层级的合成技术。 RTL可协助提升设计者的生产力,但它同时也需转换成以RTL为基础的设计输入、验证,并接受最佳化技术的可预测性限制。这些关键技术通常是累积而成;也就是说,它们是相互依存,以便对生产力造成综效的改善。另外,它们也还要包容先前采用不同设计方法的旧设计存档。

主要设计方法

如(图二)之说明,现今采用的设计方法可区分为时序驱动设计(Timing Driven Design,TDD)、以方块为基础的设计(Block Based Design,BBD)及以平台为基础的设计(Platform Based Design,PBD)等三类模式。三者的区隔则视其所使用的关键技术、设计容量,以及对设计再利用的投资及层级而定。

然而,上述三种模式的每一区隔间,仍有灰色地带存在,其间还是可发现某些特定的设计族群。另外,设计方法的转换过程,本质上是依序发生的。从TDD移往PBD是一个多重步骤的过程。虽然较大的投资与更精确的目标可以减少整体的转换时程,但是一个BBD实验基础仍是升级至PBD不可或缺的要素。

| 《图二 主要设计方法》 - BigPic:685x336 |

|

各种设计方法简介

时序驱动设计(TDD)

时序驱动设计(TDD)是用来设计中型规模及复杂度ASIC的最佳方法,主要是针对DSM处理器周围的逻辑组合。只用到极少的再利用方块,因此不需要阶层式(Hierarchical)设计组织架构。以时序(Timing)、晶元大小或电源等限制条件驱动的RTL至矽晶片设计流程,具有相当大的时效风险。

传统上,这是透过在RTL验证完成前的良好实体设计来管理的。若要在扁平式(Flatten)晶片制作环境下成功地执行一致的设计,即需用到改变管理与平面图控制技术,这可将RTL中不可避免的「最后一只虫」结合至实体设计,并保持TDD的最佳化结果。

以区块为基础的设计(BBD)

系为了因应设计复杂度增加、系统、RTL与实体层间的新关系、电路再利用等因素而创造的模式。理想上,BBD是系统层级的行为模型所建成,这也是软硬体取舍及使用软体模拟或硬体仿真的软硬体功能,协同验证设计执行的关键位置。

新的设计元件随后会被分割,再安排到特定功能的RTL方块;接着依照预定的时序、电源及面积等限制条件进行设计工作。这与TDD采用的方法正好相反,TDD中的RTL是沿着合成规则的界限逐步构筑而成;在有限的应用空间中(高度的演算法则),行为合成将与资料路径搭配,以发展出更新的功能。

一般而言,BBD中许多再利用的功能阶无需进一步再修正或再验证。可编程处理器核心(如DSP,微控制器或微处理器),将会以可预测,预先验证过的硬体或韧体(电路单或平面规划)方块;或是可修改,重新验证的RTL档案等型式读入设计环境内。

这种高复杂度的设计,通常都会采用汇流排型式的架构,汇流排可能由处理器决定或由用户自订。此外,也还会应用到非常普及的扁平制造测试架构。而全部或部份扫描,以多工器为基础及内建自我测试(BIST)等方式都有可能,端赖覆盖率、可制造性及面积/成本等因素的综合考量。

不管是在阶层式或扁平式内容下,都一定要执行时序分析。由上而下的规划会产生个别方块的预算,交由合成工具层层地分析各部份的时序。设计人员之后可选择扁平式或阶层式最终绕线莘取结果。除此之外,再视该设计所要求的精确度,决定扁平式或阶层式的详细时序分析。

设计需求中也包含精确度的误差范围,或达到设计敛的保护带,此一保护带的管理将是DSM设计中最重要的成败关键。由于BBD需要一个有效率的方块层级平面规划工具,以便快速地估算出RTL的方块大小;而为所有方块及其内部连线建构合理的延迟预算,则是确保达到收敛的基本条件。使用能理解实体设计限制的合成工具,更能有助于增加收机率。

在BBD设计中,设计小组与ASIC厂商之间的文件交接,经常发生在比TDD还低的设计层级。一个完整布线的电路单(Netlist)或GDSII,都是可能的做法。虽然RTL交接非常吸引人,但经验显示,唯有在产品研发及ASIC厂商的设计人员共同合作的模式下,才会有效。若是缺乏预先验证过的固定特性方块,作为主要设计内容,RTL交接对大部份积极的设计案件都是不切实际的。

以平台为基础的设计(PSD)

为更进一步的技术演进。 PBD包括TDD与BBD技术所累积的能力,外加密集的设计再利用及设计阶层(Hierarchy)观念。针对新开发的产品,PBD可减少整体的TTM(Time-to-Market),扩大机会及加快推出后续产品的速度。与BBD相同,PBD是一种由系统层级开始的组织层级式设计方法。

PBD与BBD的最大差异,在于PBD经过多方面,有计划的设计再利用考量以达到最高生产力的要求。生产力的提升是因为采用具有标准异面的可预测、事先验证过之功能方块。设计再利用的设计方法愈周延,功能方块的改变就愈少。 PBD设计方法将设计分为两部份,一是方块创作,另一个则是晶片系统整合。

◆方块创作

主要是采用适合该方块型态(TDD、BBD)的设计方法,而该方块往后又能轻易地与多重目标的设计结构连接。为了发挥效益,就必须先建立介面标准与虚拟系统设计两个主要观念。

◆系统晶片整合

着重于设计,验证系统架构与方块间的介面。从方块创作到系统整合间的递送是标准化的(类似VSI或VSI基础的变形)、多层级的,直接显示从系统到实体理论的设计程序。

整合作业从分割围绕在事先即已存在的方块层级功能之周边系统开始,同时确认新的或所需的差异化功能。在系统层级完成分割动作后,再依续执行效能表现分析,硬体/软体设计取舍及最后的功能验证等设计工作。

PBD主要是使用轫式或硬式的可预测、事先验证过的功能方块。这些方块可做成软式的电路档,再做为制程演变的推进器。在某些情况下,为保障安全及降低复杂度,制造商会将硬式虚拟元件(Virtual Component,VC)的详细实体特性加以整合。

轫性虚拟元件(VC)会被用来表示设计长宽比的弹性,而硬式VC则是用来制作晶片主要的最佳化功能。某些方块创作可提作其轫式及硬式VC的多重长宽比选择,以减少配置时的难度。少部份的关键性介面与支援功能,则可以软式VC代表,并在整合过程中融入设计内。

对PBD而言,设计人员与晶圆供应商之间的交接范围会变得更为宽广。 PBD与BBD很类似,均使用Customer Owned Tooling(CoT)为基础的电路单(Netlist)/GDSII交接方式。但无论如何,当设计逐渐由可预测、事先验证过的可再利用方块主导之后,RTL签认(Sign-Off)的改变将有极大成功的机率。

RTL Sign-Off成功与否取决于晶圆厂在其制程上,处理DSM特殊现象及满足客户对TTM强大压力的态度。举例而言,在只有六个月的设计周期内,要占用3~5个月的实体设计期间,这是绝对无法接受的安排。

| 《表一 IC制程技术的演进》 - BigPic:692x187 |

|

再利用-SoC设计的成败关键

当设计模式跨入SoC型态后,TTM(Time-to-Market)会主导产品的计划与开发时限。半导体厂商的技术蓝图,均表明「设计分享」为规划未来方向的最高方针。设计再利用在短程中可领先对手;中长程来看则是生存的必备之路。因此当VSI联盟着手播种SoC产业时,即有许多公司开始开发不只与VSI提案相容,更可根本改变其设计流程的,跨公司间相互再利用的解决方案。

调查发现,即使是某一公司自行开发使用的专属IP,也未必能成功地再利用于特定的工具、制程或技术之上。唯有建立一套涵盖IP整合、创造、取用、保护、价值确认、移动与支援的系统,才能真正享有生产力的优势。必须先有看得到的IP系统研发计划,始能知道要创造什么、购买什么、重行设计什么、使用何种标准与打破什么障碍等答案。

「再利用IP」一直以来都是快速提升生产力的基本口号。业界盛传的一些术语,如设计工厂(Design Factory),或晶片组装(Chip Assembly)等;就好像福特汽车的生产线可以将从前设计的零件,或其它地区、公司制造的半成品,组装成一部汽车那么神奇。然而二十多年来,经过无数电子工厂与软体设计公司管理阶层的种种努力,所得到的成效还是极为有限,仍旧还有许多承诺无法实现。

究其原因,大家都知道再利用一定可行,并且效果显著。以基层的观点来看,做完一项工作的团队在做第二次时,生产力明显会更佳。因此,再利用的知识明显地潜藏在设计人员的脑中,以及他们使用过工具、制程与技术的经验中。若是另组一个团队重做同样的工作,则无法提升任何生产力,这是由于新团队无法累积经验之故。IP再利用的困难来自技术、组织及文化障碍等各个层面,惟有定义清楚可行的再利用模式、法律规范、商业惯例与管理准则,才有大量普及应用的机会。

SoC与生产效益

SoC的成功,需要许多不同条件的共同配合。可由制造与测试角度来支援小于0.2微米设计的制程改良晶片技术仍持续进行之中。同时,创造与整合晶片的设计工具与流程还未达成熟之境,甚或尚未推出。即使在此种种困难环境下,仍有两项新兴的核心设计技术可点出SoC的生产力效益。

这两项新兴技术分别为整合平台与介面为基础的设计方法。它们同时代表了设计原理、工具、架构、方法与管理的整体融合。当大部份的半导体制造、设计与工具厂商,都接纳并依据上述技术规划整体作业环境后,必定能见到更多SoC产品问市,带给消费者更大的科技应用空间。

(本文作者为荷商益华台湾分公司行销总监)