二氧化铪(HfO2)具铁电相(ferroelectric phase)的这项新发现,已再次引起半导体界对铁电材料记忆体的兴趣。具非挥发性且以二氧化铪为基础的铁电场效电晶体(ferroelectric field-effect transistor,FeFET)便是个例子,它展现了3D NAND记忆体类型储存应用和记忆体内运算(in-memory computing)的特性。爱美科技术总监Jan Van Houdt将解释FeFET运作机制,以及预测这项令人振奋的「新选手」会怎样融入下一代记忆体的发展蓝图。

铁电场效电晶体:具备记忆的电晶体

铁电体(ferroelectrics)是一种材料,其晶体展现了自发电极化的现象。铁电体可能处在二元状态(二态),可透过外部电场逆转。当施加外部电场时,铁电材料晶体内形成的电偶极往往会自行平行于电场方向。当外部电场移除时,铁电材料会保持在极化状态,这也让铁电材料具备非挥发性。铁电材料的极化电荷和外加电场有非线性的关系,也让铁电的极化-电压(polarization-voltage,P-V)特性呈现迟滞回路(hysteresis loop)的形态。

| 图一 : 铁电体(ferroelectrics)晶体展现了自发电极化的现象。铁电体可能处在二元状态(二态),可透过外部电场逆转。 |

|

为了发展DRAM类型的记忆体应用,铁电材料正在开发中—铁电被用来当作DRAM电容器的介电质。但其实也可以把铁电材料用来代替高介电常数金属闸极电晶体(high-k/ metal-gate transistor)的闸极介电质,最终会制成一种非挥发性的电晶体,也就是铁电场效电晶体(ferroelectric field-effect transistor),或称FeFET。

现在运用铁电材料制成的闸极绝缘体,其两种稳定的残余极化状态会改变电晶体的临界电压,即使移除供电电压也是如此。因此,此二元状态会被编写在电晶体的临界电压中。要将资料写入记忆体记忆单元,可以在电晶体的闸极施加脉冲,闸极会改变铁电材料的极化状态,并影响临界电压。

举例来说,施加正脉冲会降低临界电压,并让记忆单元的电路处在「开」的状态。而读取资料则是透过测量汲极电流。这种记忆体运作模式和NAND Flash的记忆单元类似,后者的电子被迫在浮闸(floating gate,FA)进出,以类似的方式影响浮闸电晶体的临界电压。

梦想成真

铁电记忆体在超过五十年前被发掘,因为它的功耗需求极低、具备非挥发性且转换(switch)速度快,一直被视为储存应用的理想技术。然而,复杂铁电材料的议题已带来严峻的考验。早期尝试的材料是基于钙钛矿族的锆钛酸铅(lead-zirconate-titanate,PZT),但要将这些材料保形沉积在电晶体上,已被证实是非常困难的。而且这些材料的介电电流极高(约300),这也阻碍了该材料和功能型电晶体的结合。

二氧化铪(hafnium-oxide,HfO2)是著名的材料,且复杂性较低,近期被发现具铁电相,让发展这项记忆体技术的想法再次被触发。研究者发现了斜方晶相(orthorhombic crystal phase),也就是铁电相,可以透过将二氧化铪掺杂到—像是矽(Si),使该相稳定。和锆钛酸铅相比,二氧化铪的介电电流较低,且能被保形沉积在薄层上。

此外,二氧化铪也是已知被用来当作逻辑元件闸极堆叠的介电材料。只要巧妙地改变这个和CMOS相容的材料,逻辑电晶体就能转变成非挥发性的FeFET记忆体电晶体。

接着…从平面走向垂直面

以二元、平面结构制成功能型FeFET已经证实可行。但二氧化铪可以制成保形的阶层,也就代表它也可能制成立体结构,像是将铁电材料沉积在垂直面的「墙」上,然后在第三维度上堆叠电晶体。

就材料而言,3D FeFET可以解决2D FeFET结构带来的一些挑战。其中一项挑战便是二氧化铪介电质的多晶性质(poly-crystalline)。扩增二氧化铪层的维度会大大限制每层的晶粒数。不同晶粒的极化方向并非全部相同,这会影响晶粒对外部电场的反应,导致高度变异性(variabilities)。藉由采用3D结构,这种限制至少能在第三维度上排除,因而削弱变异性,并让数据更好控管。

垂直式FeFET技术和3D NAND类型的制程相容,后者一直是爱美科努力实现的方向。 3D NAND Flash是当今主流的高密度资料储存媒介,其价位相对便宜,且具非挥发性,但缺点是结构复杂,且运作速度慢。

和复杂的3D NAND Flash相比,这些垂直式FeFET预计会有几个好处,包括更简化的资料处理流程、更低的功耗以及更高的处理速度。相较于3D NAND Flash,垂直式FeFET可能以更低的电压进行编程(大约4V,而NAND是20V),这也提升了可靠性和尺寸扩充性。

最初结果:2V记忆体窗、类似Flash的耐用性

爱美科从几年前开始便一直专注于开发3D NAND类型的垂直式FeFET,因此,爱美科也运用他们发展进阶3D NAND Flash技术的杰出经验,并结合早期研究以锆钛酸铅为基础的铁电材料记忆体时所用的工具、背景和载体。自2016年起,爱美科和合作伙伴们建立了产业合作计画,共同研究垂直式FeFET。

在该计画的架构下,研究团队主要处理3D FeFET在资料处理、特性分析(characterization)和可靠性方面的挑战。举例来说,该团队正在建立如何稳定二氧化铪斜方晶相(即铁电相)的技术诀窍。该相可透过像是矽在二氧化铪层进行替代性掺杂(substitutional doping)来获得。这样能在该薄层产生应变(strain),让晶体呈现预期的斜方晶相。

矽被视为较合适的掺杂原子是因为其热积存(thermal budget),也就是说,它能保留铁电相,但该团队也在研究其它替代掺杂物,诸如铝(Al)和镧(La),同时研究铪锆基氧化物(hafnium-zirconium-oxide),以作为替代的铁电材料。

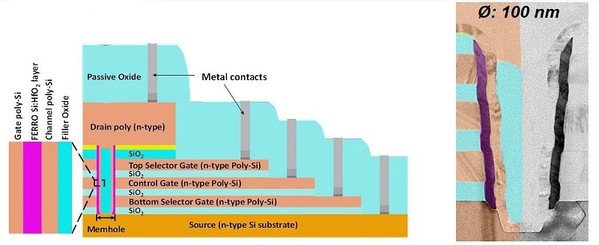

爱美科近期展示了首个功能型垂直式二氧化铪FeFET,其结构为通心面形状的3D NAND。该元件根据爱美科处理3D NAND Flash的流程来制造,目前还取代了传统的ONO介电层(oxide-nitride-oxide),改采用8nm且掺杂矽的二氧化铪层,以原子层沉积法沉积(atomic layer deposition,ALD)。多晶矽被用来当作闸极材料,而非晶矽则是通道。

该测试载具(test vehicle,TV)包含了一垂直弦,让三个闸极(控制闸极、底部和顶部选择器闸极)串联。该弦内部的孔洞先以氧化物填满,再掘入内凹(recess),因此结构看似通心面。在真实的3D NAND类型元件中,在垂直方向上的控制闸极数量可多达64个,以实现高密度记忆体解决方案。

| 图三 : 图左为通心面型的3D FeFET切面示意图,可见三个记忆单元串联;图右为穿透式电子显微镜(transmission electron microscopy,TEM)下的切面图(直径:100nm)。 |

|

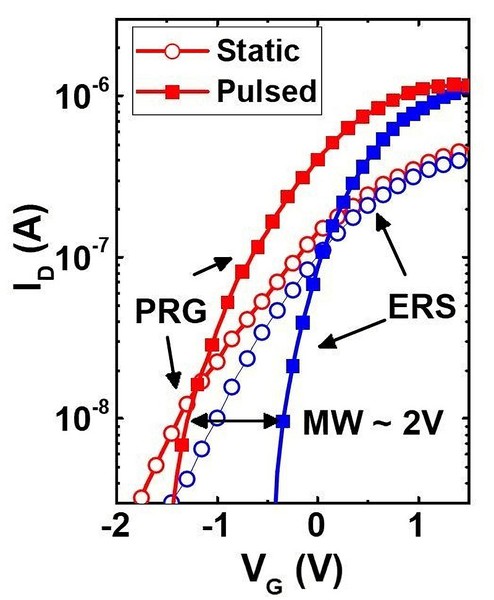

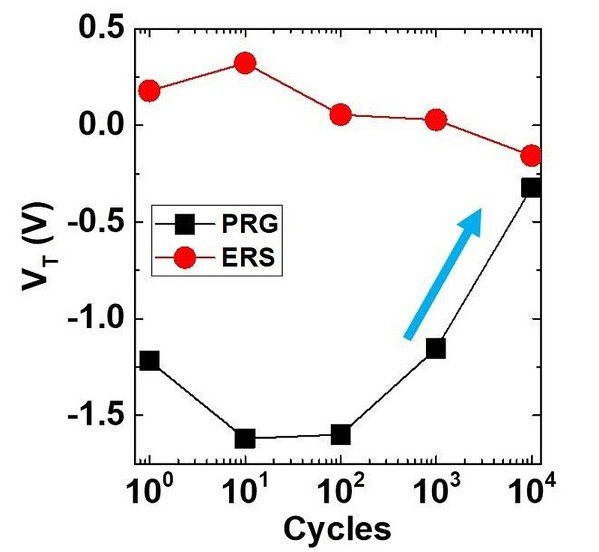

就此测试载具来说,在施加100ns的写入/擦除脉冲后,可获得将近2V的记忆体窗。 FeFET也展现了85℃的资料储存能力(retention):在摄氏85度下运行100小时,二元状态的区分还是很明显。该研究团队也表示FeFET的耐用性高达10的4次方,和Flash相似,且已完成首次可靠性测试。由施加在介面的高电场造成的电荷捕捉现象限制了FeFET的重复擦写能力(cycling performance),这点也被提出来讨论。减少介面层的厚度可能可以处理这个问题。

| 图四 : 记忆体特性分析:至多高达2V的记忆体窗能在施加100ns写入/擦除(PRG/ERS)脉冲後获得。 |

|

| 图五 : 可靠性特性分析:临界电压(threshold voltage,VT)和循环次数在写入和擦除後的发展。记忆体窗的结束发生在10的4次方的次循环之後。 |

|

3D NAND类型的应用及机器学习

FeFET还处在研发的早期阶段,要断言量产可不可行或何时达成都还言之过早。但这项富前瞻性的新记忆体概念已引起产业要角浓厚兴趣。而爱美科的角色便是探索FeFET的最大潜能,并让合作伙伴在该研究领域能领先起步,进而让他们做出决策要如何让FeFET最佳化地融入其产品和晶片。

FeFET作为一种可独立运行的记忆体,据信将成为储存级记忆体(storage class memories,SCMs)的一员,就字面上来说,也代表它将弭平DRAM和NAND Flash的界线,前者速度快且具挥发性,后者速度慢、具非挥发性且密度高。 FeFET是非挥发的,相较于NAND Flash,它还有几个优点:FeFET转换速度较快、资料处理更简易、功耗较低,且有潜力能以更低压运作。然而,虽然就速度而言,FeFET更接近DRAM,但FeFET的重复擦写能力(为10的4次方,而DRAM为10的12次方)有限,这很可能会让它在DRAM和NAND这条分界上更倾向NAND那方。

FeFET记忆体在逻辑元件代工厂领域也引起注意,因为FeFET的高速特性很可能有利于机器学习应用—此应用需依靠记忆体内运算(in-memory computing)来达成。因此,目前有好几种记忆体在探索该应用,包括Flash、磁阻式随机存取记忆体(magnetic RAM,MRAM)、电阻式随机存取记忆体(resistive RAM,RRAM)、相变记忆体(phase change memory,PCM)、静态随机存取记忆体(static RAM,SRAM)和FeFET。因为FeFET的非线性特性和速度,它成为额外引人注目的技术,用来开发以深度学习卷积神经网路运转的机器学习应用。就这类应用,平面式的FeFET很可能会先出现。

展望:迈向更高密度FeFET之路

NAND Flash技术的其中一项特别优势是:其记忆单元的容量最高为4位元,这也使得该技术拥有独一无二的高资料密度。在传统的单阶记忆单元(single-level cell,SLC)中,每个记忆单元能处于二元状态中的其中一种,且每记忆单元储存1位元的资料。工业型NAND Flash已从单阶记忆单元进化,每记忆单元已可储存2位元、3位元甚至4位元的资料。每单元储存4位元的记忆体需在每个电晶体中编设16个临界电压状态,使得所需记忆体窗变得庞大。

但就FeFET而言,爱美科认为有三种方式能提升其资料密度,并使之成为能与NAND Flash竞争密度的强劲对手。首先,如果临界电压能维持充分稳定状态,FeFET的2~2.5V记忆体窗原则上能达成每记忆单元2位元的编程,也就是说,每个电晶体需配置4个临界电压状态。

第二,透过采用类沟槽(trench-like)的结构来连结电晶体,每记忆单元的资料密度就可以翻倍,沟槽的两边各配置两颗电晶体。在现今的3D FeFET设计中,像是爱美科的通心面型NAND结构,控制闸极是以环绕式闸极结构(gate-all-around structure,GAA structure)来设计。这表示闸极被通道包围,限制了电晶体数量,每层和每弦仅一颗。环绕式闸极结构在NAND Flash是必需的,是因为要用来改善浮闸或氮化矽捕陷层的电荷注入,但FeFET并无此需求。

爱美科目前正在探索能替代类沟槽结构的选项,以实现在沟槽侧壁上堆叠电晶体,而现在的电晶体分别放在沟槽的头尾。此新型架构应该会让记忆单元的密度高出一倍,还会降低记忆单元间的变异性。

第三,FeFET记忆体单元可能会微缩至更小的尺寸。在传统的NAND Flash记忆单元内,ONO介电层的厚度约为20nm。但在FeFET记忆单元中,二氧化铪铁电层预估能微缩至4nm。此外,在垂直方向上,因为FeFET的工作电压比NAND Flash还低,FeFET的字元线距会比较短。

总而言之,3D FeFET拥有多条迈向高密度的发展之路,同时也会朝向高速、非挥发、类似Flash的耐用性、低工作电压和低功耗这些面向发展,这些潜能在在使得3D FeFET成为对战3D NAND类型应用的强劲选手。

(本文由爱美科授权刊登,作者Jan Van Houdt为爱美科半导体科技与系统部技术总监;编译/吴雅婷)