迎合現今AI熱潮對於先進邏輯和記憶體需求,由比利時微電子研究中心(imec)協調整合的歐洲研究計畫奈米晶片(NanoIC)試驗製程,持續致力於加速2奈米以後的晶片技術創新。近日更宣布推出兩套全新製程設計套件(PDK),包含用於先進邏輯微縮技術的14埃米(A14)路徑探尋PDK,以及用於先進記憶體創新的嵌入式DRAM(eDRAM)系統探勘PDK。

|

| 目前由eDRAM PDK提供一套探索嵌入式記憶體解決方案的虛擬平台,可填補外接DRAM與內建SRAM之間的技術缺口。 |

透過免費開放這類NanoIC試驗製程的先進PDK在推進半導體創新方面發揮關鍵作用,連接早期階段的研究探索與現實世界的整合。將有機會讓設計人員在新興技術的硬體問世之前,提早取得實際的設計規則和實作工作流程;並提供使用者和新創公司探索先進技術節點和嵌入式記憶體設計的獨特管道,預測整合挑戰和參照實際的微縮指標,為設計進行基準測試。

作為首批推出的製程設計套件,A14路徑探尋PDK提供用來探索14埃米節點的視覺設計環境,用於新興微縮加速器的晶背金屬接點。此有別於過去2奈米(N2)製程設計套件,運用中段製程矽穿孔封裝(TSVM)的結構來支援晶背供電,14埃米節點進一步採用更緊湊的直接晶背接點方案來取代TSVM。

這套新架構直接從晶圓背面建立連接到閘極的電源佈線,還不需要晶圓正面的複雜金屬佈線,成功在相同頻率和單元密度下,達到比2奈米更低的IR壓降、提供18%面積增益和減少7%功耗。該套件包含完整的162-SDC元件庫,並獲得兩大電子設計自動化(EDA)廠商益華電腦(Cadence)、新思科技(Synopsys)的支持。

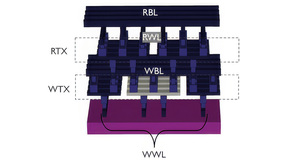

此外,為了有助於推動A14 PDK探尋邏輯路徑,NanoIC試驗製程也推出首款eDRAM系統探勘PDK,以提供具備高密度及低延遲的內建記憶體,拉近記憶體與處理單元的距離,也是在先進運算架構縮短延遲和改良功率效率的關鍵策略。

目前由eDRAM PDK提供一套探索嵌入式記憶體解決方案的虛擬平台,可填補高密度但高功耗的外接DRAM,與高速但尺寸受限的內建SRAM之間的技術缺口。利用eDRAM PDK聚焦資料密集和AI運算的系統級表現,可讓設計人員藉此評估用來縮短高密度記憶體與處理器、圖形處理器(GPU)之間距離的新興記憶體架構和整合策略,減少資料傳輸距離,改良能源效率,以及提升整體系統性能。

展望未來,eDRAM PDK將發展成一套完整的系統探勘平台。這一步發展將能讓設計人員突破虛擬驗證,並分析完整的系統級交互作用,更深入研究嵌入式記憶體這類用於AI與資料密集運算的關鍵元件。隨著平台趨向成熟,未來的研發階段包含硬體驗證,還有最終在NanoIC試驗製程進行原型設計和投片(tape out)的發展機會。